# ICS User's Guide

Revision 20.1

DOC10094-1LA

# ICS User's Guide

**First Edition**

by

Les Acton Updated for Revision 21.0 by

Les Acton

This guide documents the software operation of the Prime Computer and its supporting systems and utilities as implemented at Master Disk Revision Level 21.0 (Rev. 21.0).

> Prime Computer, Inc. Prime Park Natick, Massachusetts 01760

The information in this document is subject to change without notice and should not be construed as a commitment by Prime Computer, Inc. Prime Computer, Inc., assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

Copyright © 1987 by Prime Computer, Inc. All rights reserved.

PRIME, PRIME, PRIMOS, and the PRIME logo are registered trademarks of Prime Computer, Inc. DISCOVER, INFO/BASIC, INFORM, MIDAS, MIDASPLUS, PERFORM, Prime INFORMATION, PRIME/SNA, PRIMELINK, PRIMENET, PRIMEWAY, PRIMIX, PRISAM, PST 100, PT25, PT45, PT65, PT200, PW153, PW200, PW250, RINGNET, SIMPLE, 50 Series, 400, 750, 850, 2250, 2350, 2450, 2550, 2650, 2655, 2755, 6350, 6550, 9650, 9655, 9750, 9755, 9950, 9955, and 9955II are trademarks of Prime Computer, Inc.

DDS (Dataphone Digital Service) is the registered trademark of American Telephone and Telegraph (AT&T).

GTE Telenet is the registered trademark of General Telephone and Electronics Corp.

This document was prepared in Australia by Technical Publications Department, Prime R&D Australia, New Industry House, Cnr. Brisbane Avenue and National Circuit, Barton, ACT 2600, Australia.

#### PRINTING HISTORY

First Edition (DOC10094-1LA) March 1986 for Release 20.1 Update 1 (UPD10094-11A) February 1987 for Release 21.0

#### CREDITS

Editorial: Marilyn Kirschen, Margaret Hill, Herb Korn Project Support: Kathe Rhoades, Dave Roberts Illustration: Terry Bacharz, Marlene Bober, Marjorie Clark, Michael Moyle Production: Michelle Hoyt Document Preparation: Margie Matteson

#### HOW TO ORDER TECHNICAL DOCUMENTS

To order copies of documents, or to obtain a catalog and price list:

United States Customers

#### International

Call Prime Telemarketing, toll free, at 1-800-343-2533, Monday through Friday, 8:30 a.m. to 5:00 p.m. (EST). Contact your local Prime subsidiary or distributor.

#### CUSTOMER SUPPORT

Prime provides the following toll-free numbers for customers in the United States needing service:

| 1-800-322-2838 | (within Massachusetts) | 1-800-541-8888 (within | n Alaska) |

|----------------|------------------------|------------------------|-----------|

| 1-800-343-2320 | (within other states)  | 1-800-651-1313 (within | n Hawaii) |

For other locations, contact your Prime representative.

#### SURVEYS AND CORRESPONDENCE

Please comment on this manual using the Reader Response Form provided in the back of this book. Address any additional comments on this or other Prime documents to:

> Technical Publications Department Prime Computer, Inc. 500 Old Connecticut Path Framingham, MA 01701

This warning applies to the 9950, the 2250, and to all other 50 Series processors manufactured after October 1, 1983:

#### WARNING

This equipment generates and uses radio frequency energy and if not installed and used properly, i.e., in strict accordance with the instructions manual, may cause harmful interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment.

Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

If there are any questions, please contact your Prime Field Office.

This warning applies to all other processors described in this book:

#### WARNING

This equipment generates and uses radio frequency energy and if not installed and used properly, i.e., in strict accordance with the instructions manual, may cause harmful interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for Class A computing devices persuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference.

Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

If there are any questions, please contact your Prime Field Office.

# Contents

### ABOUT THIS BOOK

### ix

# 1 HARDWARE COMPONENTS

| Introduction                     | 1-1  |

|----------------------------------|------|

| Controller Board                 | 1-4  |

| General Description              | 1-4  |

| Microprocessor and Support Logic | 1-6  |

| Microprocessor Bus (uBus)        | 1-7  |

| ICS3 Controller Board LED Lights | 1-7  |

| Memory                           | 1-7  |

| Input/Output Devices             | 1-8  |

| LAC Card Cage Assembly           | 1-13 |

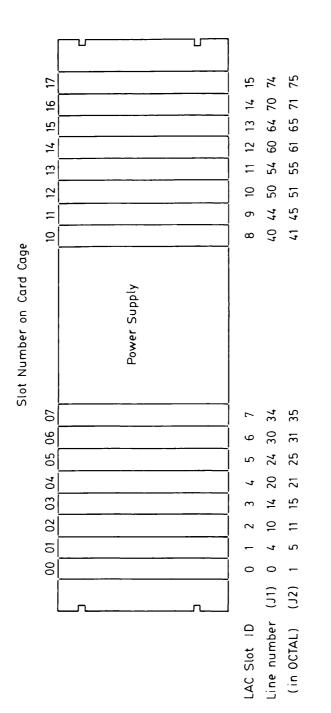

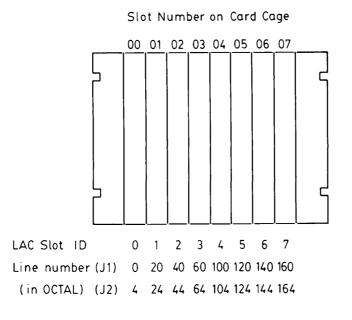

| 8-LAC ICS3 Card Cage             | 1-13 |

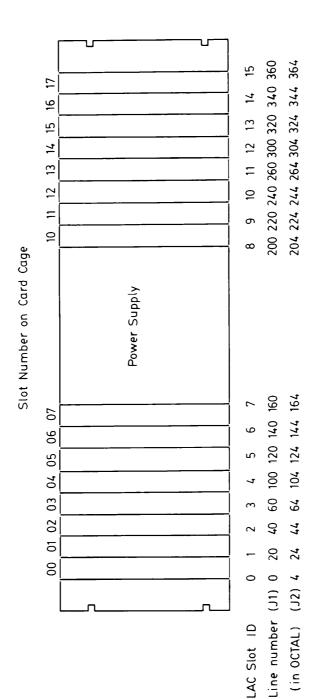

| 16-LAC ICS3 Card Cage            | 1-13 |

| ICS2 Card Cage                   | 1-14 |

| Buffer Board                     | 1-14 |

| Asynchronous RS232 LAC           | 1-15 |

| Synchronous LAC                  | 1-18 |

| Power Supply Card                | 1-19 |

| LAC Bus                          | 1-19 |

| External Interfaces and Cabling  | 1-19 |

| EIA RS232/CCITT V.24             | 1-20 |

| CCITT V.35/DDS                   | 1-20 |

| Environmental Specifications     | 1-21 |

# 2 ICS2/3 SOFTWARE

| Introduction                           | 2-1  |

|----------------------------------------|------|

| ICS2/3 — PRIMOS Software               | 2-2  |

| PRIMENET/X.25 Support Software         | 2-4  |

| RJE Support Software                   | 2-6  |

| ICS2/3 Operating System                | 2-8  |

| The Kernel                             | 2-9  |

| Cold Start                             | 2-11 |

| Warm Start                             | 2–12 |

| IBC Microcode                          | 2-12 |

| User Protocol-specific Modules         | 2-14 |

| X.25 Protocol-specific Modules         | 2-14 |

| RJE Protocol-specific Modules          | 2-19 |

| SDLC Protocol-specific Modules         | 2-23 |

| Asynchronous Protocol-specific Modules | 2-28 |

# 3 PRIME HOST SOFTWARE

| Introduction                            | 3-1  |

|-----------------------------------------|------|

| PRIMENET/X.25 in Prime Host             | 3-1  |

| Initialization                          | 3-2  |

| Startup                                 | 3-2  |

| Active Processing                       | 3-3  |

| Shutdown                                | 3-3  |

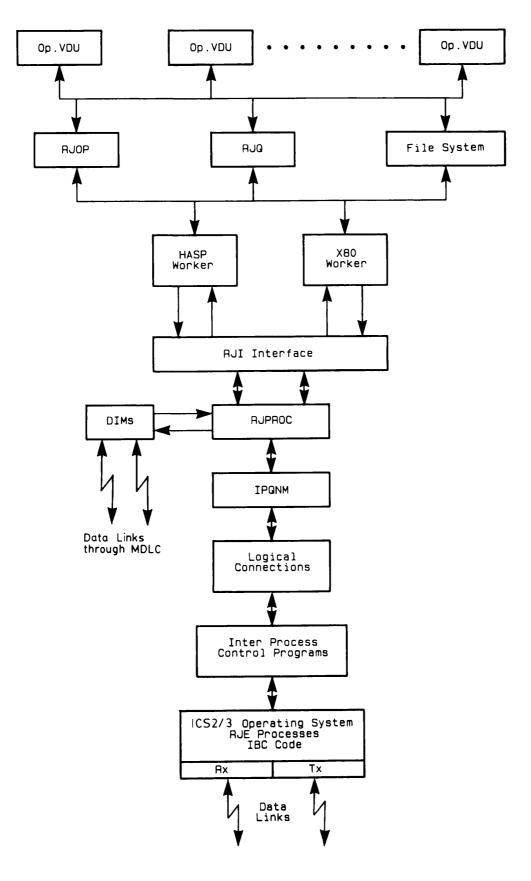

| RJE Protocol in Prime Host              | 3-5  |

| RJO                                     | 3-5  |

| RJÕP                                    | 3-5  |

| The Worker Process                      | 3-5  |

| RJI                                     | 3-5  |

| RJPROC                                  | 3-7  |

| IPONM                                   | 3-7  |

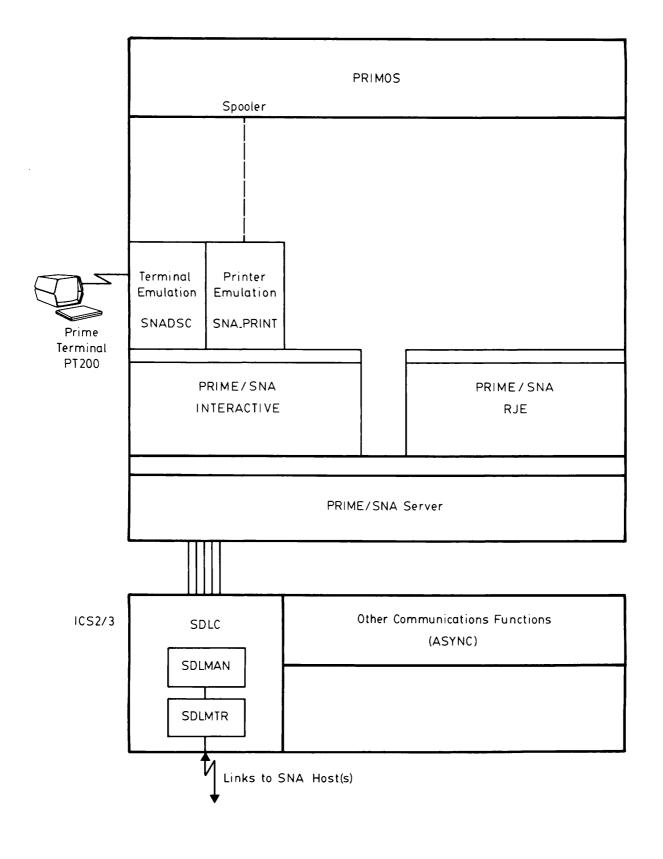

| SDLC Support From the Prime Host        | 3-7  |

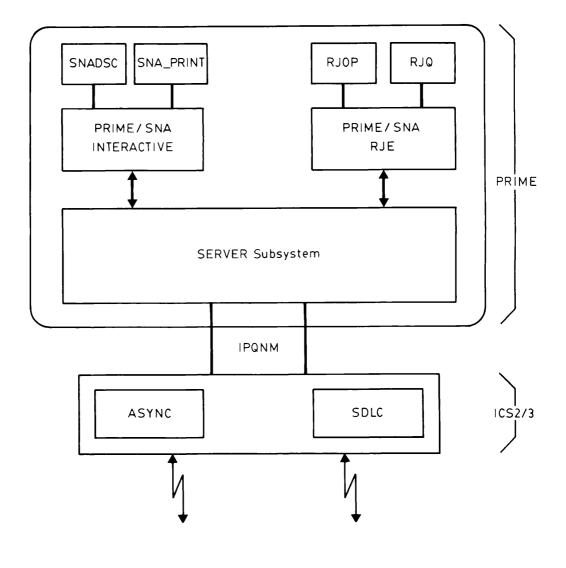

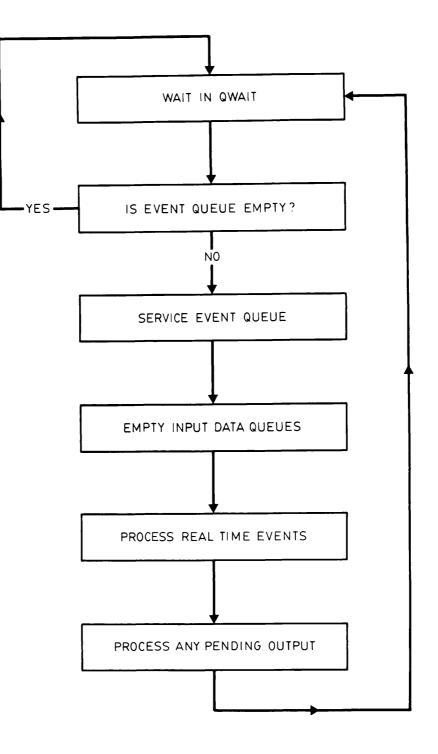

| PRIME/SNA Server Subsystem              | 3-7  |

| Other PRIME/SNA Components              | 3-8  |

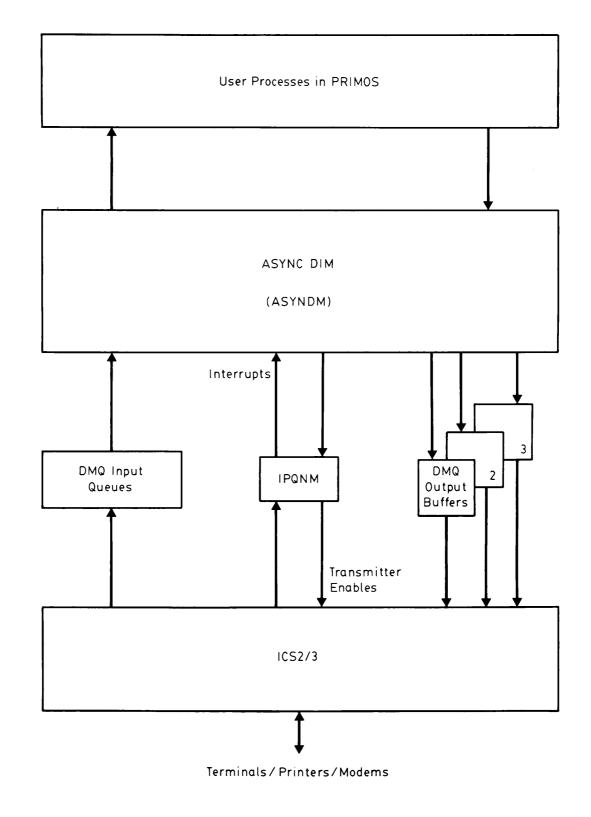

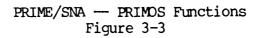

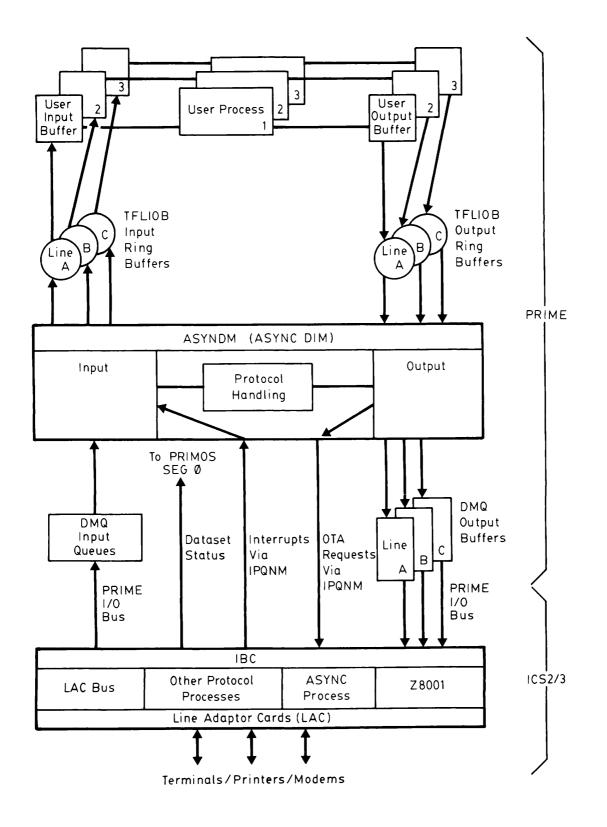

| Asynchronous Protocol in the Prime Host | 3-10 |

| Data Flow Between ICS2/3 and PRIMOS     | 3-10 |

| ASYNDM Process                          | 3-10 |

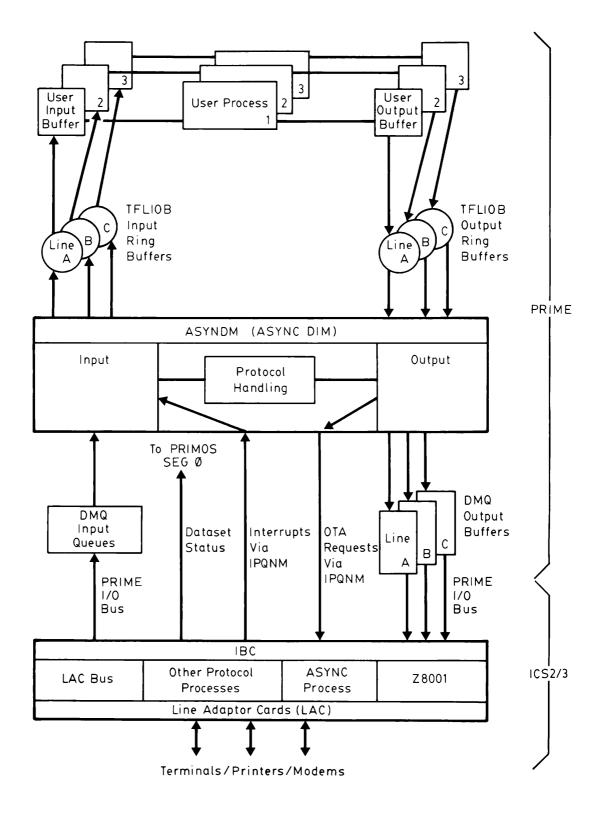

| ICS ASYNDM Code Flow                    | 3-12 |

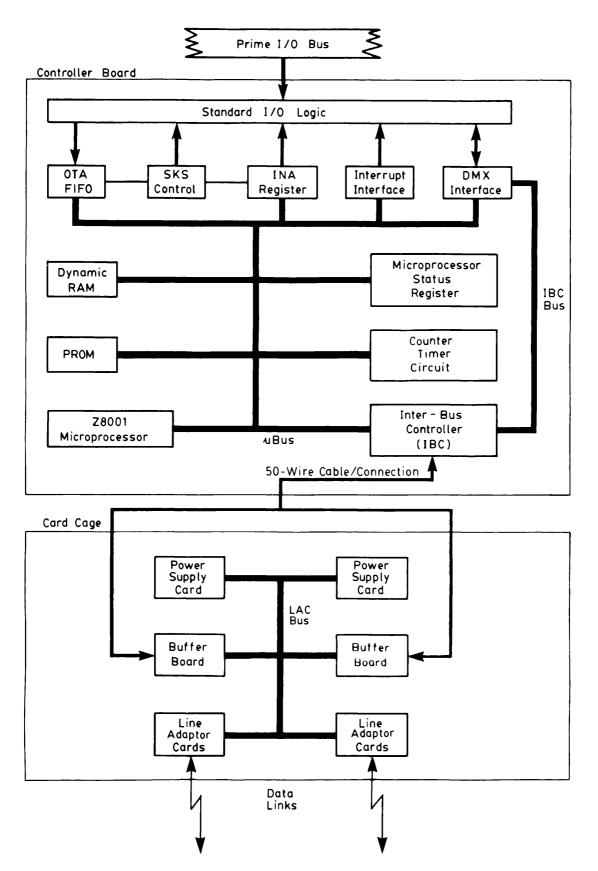

# 4 ICS2/3 SYSTEM ARCHITECTURE

| Introduction                      | 4-1 |

|-----------------------------------|-----|

| ICS2/3 Hardware Architecture      | 4-1 |

| PRIMENET/X.25 System Architecture | 4-3 |

| RJE System Architecture           | 4-5 |

| SDLC System Architecture          | 4-7 |

| Asynchronous System Architecture  | 4-9 |

# 5 CONFIGURATION

| Introduction                      | 5-1  |

|-----------------------------------|------|

| Hardware Configuration            | 5-2  |

| Controller Board                  | 5-2  |

| Buffer Board Cabling              | 5-5  |

| Buffer Board                      | 5-6  |

| LAC Bus Backplane                 | 5-7  |

| LAC Bus Power Supply              | 5-7  |

| LAC Card Cage Assembly            | 5-14 |

| LAC Slot Addressing               | 5-23 |

| LAC Priority                      | 5-24 |

| Software Configuration            | 5-24 |

| Configuration Directives          | 5-24 |

| Valid Protocol Token Combinations | 5-27 |

| Configuration Directives          | 5-24 |

| PRIME/SNA (SDLC) Configuration         | 5-33 |

|----------------------------------------|------|

| Server Subsystem Configuration         | 5-34 |

| Invoking/Starting the Server           | 5-34 |

| PRIMOS Directives and Commands         | 5-35 |

| Asynchronous Configuration             | 5-36 |

| Asynchronous Lines                     | 5-37 |

| Difference Between ICS2 and ICS3 LACs  | 5-37 |

| Asynchronous LAC Slot Addressing       | 5-37 |

| Asynchronous Directives for the ICS2/3 | 5-38 |

| ICS CARDS Directive                    | 5-29 |

# 6 PERFORMANCE AND RESTRICTIONS

ţ

| Introduction<br>Protocol Performance<br>ICS2 — Prime Interface<br>Z8001 Software Performance<br>IBC Software Performance<br>Line Speeds | 6-1<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4 |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Effects of ICS2/3 Overload                                                                                                              | 6-5                                    |

| Calculating Performance                                                                                                                 | 6-5                                    |

| Example                                                                                                                                 | 6-6                                    |

| Calculations                                                                                                                            | 6-6                                    |

| Calculation Summary                                                                                                                     | 6-8                                    |

| Restrictions                                                                                                                            | 6–10                                   |

| PRIMENET/X.25 Restrictions                                                                                                              | 6–10                                   |

| RJE Restrictions                                                                                                                        | 6-11                                   |

| SDLC Restrictions                                                                                                                       | 6-12                                   |

| Asynchronous Restrictions                                                                                                               | 6-12                                   |

| Restrictions on the Protocol                                                                                                            |                                        |

| Combinations Supported                                                                                                                  | 6-13                                   |

# 7 DIAGNOSTICS

| Introduction       | 7-1 |

|--------------------|-----|

| Stage 1 Diagnostic | 7-1 |

| Stage 2 Diagnostic | 7-4 |

# 8 DYNAMIC DLL/ULD MECHANISM

| Introduction<br>Implementation           | 8-1<br>8-2 |

|------------------------------------------|------------|

| COMM_CONTROLLER Command                  | 8-2        |

| Command Syntax Checking                  | 8-4        |

| Example of Using COMM_CONTROLLER Command | 8-8        |

| Messages                                 | 8-8        |

| Restrictions                             | 8-14       |

| DSM Logging by ICS Boot Servers          | 8-15       |

| Enabling DSM Logging                     | 8-15       |

| DSM Log File                             | 8-15       |

| Messages Logged to DSM                   | 8-16       |

| DISPLAY_LOG Examples                     | 8-17       |

9 BATTERY BACKUP

Battery Backup 9-1

#### APPENDICES

A ICS2/3 CABLES AND CONNECTORS

#### B ERROR AND STATUS MESSAGES

|   | Introduction<br>Downline Load Sequence<br>Controller Status<br>Downline Load Error Messages<br>PRIMENET/X.25 Error Messages<br>Error Messages During Initial Startup<br>PRIMENET/X.25 Normal Operation<br>RJE Error Messages<br>Errors in RJE Line Enabling<br>RJE Normal Running<br>SDLC Error Messages<br>Asynchronous Error Messages<br>Error Summary Tables | B-1<br>B-2<br>B-3<br>B-4<br>B-11<br>B-11<br>B-17<br>B-20<br>B-20<br>B-23<br>B-29<br>B-37<br>B-42 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| С | GLOSSARY                                                                                                                                                                                                                                                                                                                                                        | Б-42<br>С-1                                                                                      |

|   | INDEX                                                                                                                                                                                                                                                                                                                                                           | X-1                                                                                              |

# About This Book

#### INTRODUCTION

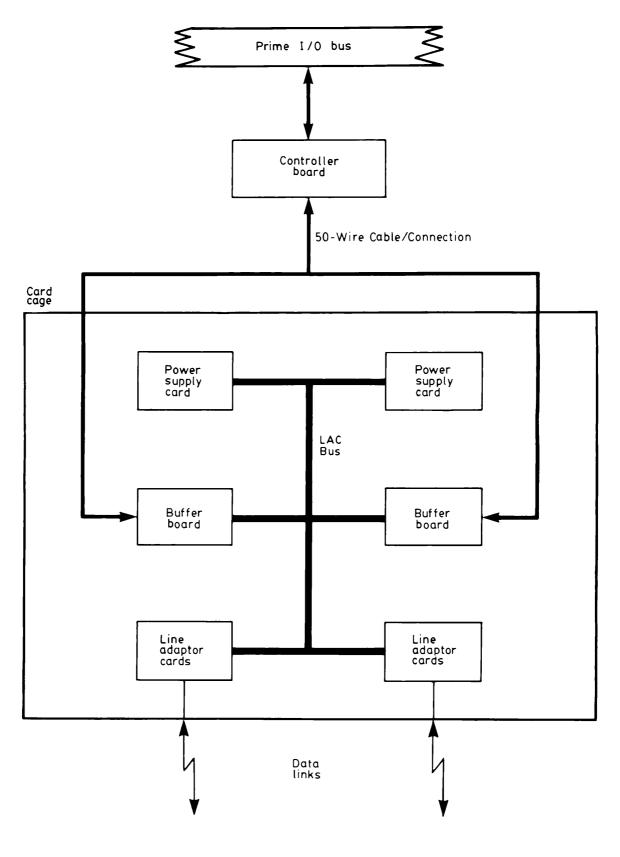

Prime's Intelligent Communications Subsystems, Model 2 (ICS2) and Model 3 (ICS3), enable a 50 Series<sup>™</sup> (host computer) to manage synchronous and asynchronous devices. The ICS2/3's ability to support asynchronous and synchronous communication lines allows a variety of communication protocols to be provided.

The ICS3 provides higher performance, more memory space, and more flexibility in the allowed protocol combinations than the ICS2 provides. The ICS3 is recommended for new installations.

The ICS User's Guide is intended for those who will be supporting the PRIMENET<sup>M</sup>/X.25 software, bisynchronous-framed RJE, SDLC, and asynchronous protocols on the ICS2/3. Users of this manual should have a comprehensive knowledge of data communication protocols.

This guide provides detailed information about the ICS2 and the ICS3. Limited information is provided on the earlier Intelligent Communications Subsystem, Model 1 (ICS1). More information on the ICS1 is contained in the references listed under <u>OTHER DOCUMENTATION</u> at the end of this section.

#### NEW FEATURES AT PRIMOS® REV. 21.0

Update UPD10094-11A describes the following new ICS facilities added at PRIMOS Rev. 21.0.

- Dynamic Downline Load/Upline Dump (DLL/ULD)

- Half duplex PRIMENET (HDX) support on ICS3 (not ICS2)

- Battery Backup support on ICS

The new dynamic DLL/ULD mechanism is described in a new Chapter 8, DYNAMIC DLL/ULD MECHANISM, together with error and status messages. Also described is the Distributed Systems Management (DSM) logging facility and sample messages.

HDX PRIMENET is mentioned in several places throughout this guide, and particularly in Chapter 5, CONFIGURATION. HDX PRIMENET support on the ICS3 controller is functionally identical to the existing support on the Multiple Data Link Controller (MDLC).

The Battery Backup facility is described briefly in a new Chapter 9, BATTERY BACKUP. There is no operator interface to this facility and it is not configurable.

#### SYNOPSIS OF THE ICS USER'S GUIDE

The ICS User's Guide contains nine chapters and three appendices.

- Chapter 1: A detailed description of the hardware components of the ICS2/3.

- Chapter 2: A comprehensive study of the various software components resident in the ICS2/3.

- Chapter 3: A short description of the software resident in the Prime host to support the various communication protocols.

- Chapter 4: An overview of the ICS2/3 system architecture.

- Chapter 5: A detailed description of the various ICS2/3 configurations that are available.

- Chapter 6: The current expected performance of the ICS2/3 under normal operating conditions, including the present communication protocol restrictions.

- Chapter 7: Details of the diagnostic tools available.

- Chapter 8: Details of the new Dynamic DLL/ULD mechanism and the DSM logging facility.

- Chapter 9: A brief description of the new Battery Backup facility.

X

- Appendix A: Information on the various types of cable used in ICS2/3 configurations, and details of some ICS2/3 edge connectors, together with their pin assignments.

- Appendix B: A listing of the possible error conditions that can occur during operational use, together with an explanation of their possible cause and how to remedy the fault.

- Appendix C: A comprehensive glossary of terms and abbreviations used in communications generally and the ICS2/3 in particular.

#### HOW TO USE THE ICS USER'S GUIDE

The following is a guide to where information is found for different categories of users:

- Category 1: The user requiring a general overview of the ICS2/3 and its relationship to other Prime products should read the introduction to Chapters 1 (HARDWARE COMPONENTS), 2 (ICS2/3 SOFTWARE), 4 (ICS2/3 SYSTEM ARCHITECTURE), 5 (CONFIGURATION), and 8 (DYNAMIC DLL/ULD MECHANISM).

- Category 2: The present user upgrading to ICS2/3 synchronous support, or the user who needs enough information to install, configure, and initialize the ICS2/3 quickly should read Chapters 5 and 8.

- Category 3: The user requiring information for fault diagnosis should read Chapter 7 (DIAGNOSTICS) and 8, and Appendix B (ERROR AND STATUS MESSAGES).

- Category 4: The user requiring detailed knowledge of both hardware and software should read, at least, Chapters 1, 2, 3 (PRIME HOST SOFTWARE), 4, and 8.

#### OTHER DOCUMENTATION

Other documentation that may be useful in understanding the ICS2/3 and its function in relation to other Prime products includes the following:

Revision 21.0 Documentation

- DOC10113-1LA Programmer's Guide to Prime Networks

- DOC10114-1LA Operator's Guide to Prime Networks

- DOC10115-1LA User's Guide to Prime Network Services

- DOC10117-1LA NTS User's Guide

- DOC10159-1LA NIS Planning and Configuration Guide

- DOC7532-3LA PRIMENET Planning and Configuration Guide

- DOC10131-1LA System Administrator's Guide, Volume I: System Configuration

- DOC10132-1LA System Administrator's Guide, Volume II: Communication Lines and Controllers

- DOC10133-1LA System Administrator's Guide, Volume III: System Access and Security

- DOC9299-3LA Operator's Guide to System Monitoring

- DOC9300-3LA Operator's Guide to File System Maintenance

- DOC9304-3LA Operator's Guide to System Commands

- DOC9298-2LA Operator's System Overview

- DOC10061-1LA DSM User's Guide

The following earlier documentation may also be useful:

- DOC10044-1LA ICS2 User's Guide, Revision 20.0

- UPD3710-32A PRIMENET Guide, Revision 20.0

- DOC5037-3LA System Administrator's Guide, Revision 20.0

- DOC7532-2LA <u>Network Planning and Administration Guide</u>, Revision 19.4

- DOC6053-3LA Remote Job Entry Phase II Guide, Revision 20.0

- DOC8908-2LA PRIME/SNA Administrator's Guide, Revision 19.4.5

- DOC8909-2LA PRIME/SNA Operator's Guide, Revision 19.4.5

- DOC8910-1LA PRIME/SNA Interactive Terminal User's Guide, Revision 19.4.1

# 1 Hardware Components

#### INTRODUCTION

The Intelligent Communications Subsystems, Model 2 (ICS2), and Model 3 (ICS3), are 16-bit Zilog 8001 (Z8001) microprocessor-based controllers, capable of supporting synchronous and asynchronous serial communication lines concurrently.

These lines can be configured to support a variety of protocols and electrical interfaces for communication with various terminal devices and controllers, other Prime computers, and the computers of other manufacturers. The ICS2/3 is supported by all current Prime 50 Series processors.

The hardware components are as follows:

- A standard Prime-size controller board

- An eight-slot Line Adapter Card (LAC) card cage for small Prime systems using the ICS3 controller board, and designed to fit inside the CPU cabinet

- A sixteen-slot LAC card cage for medium to large Prime systems using either the ICS2 or ICS3 controller board, and designed to fit in a peripheral cabinet

- A smaller sixteen-slot LAC card cage for medium to large Prime systems using the ICS3 controller board, and designed to fit inside some CPU cabinets or a peripheral cabinet

- A 50-wire cable to connect the controller board to the buffer board in the LAC card cage, either directly or via the Prime bulkhead

- Cables to connect ICS2 LACs to the Prime peripheral bulkhead, and then, to users' terminals, printers, and modems

- Cables to connect ICS3 LACs (using their integral bulkheading) directly to users' terminals, printers, and modems

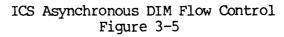

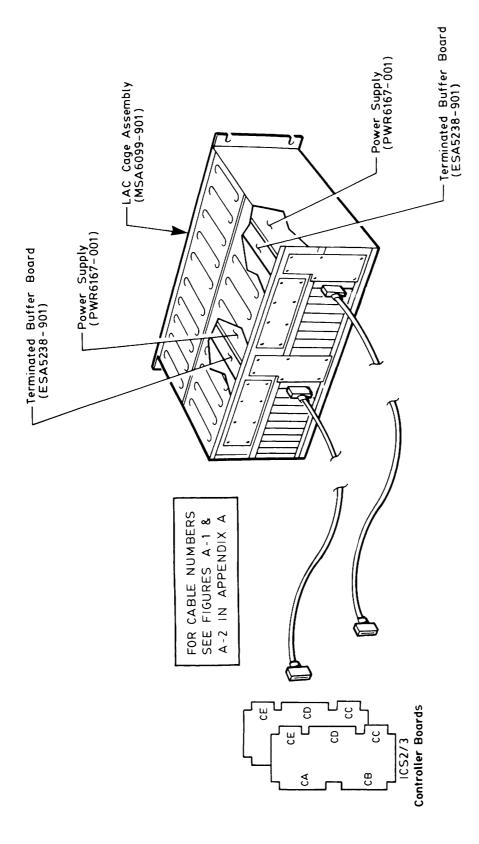

An overall block diagram of the ICS2/3 is shown in Figure 1-1.

#### CONTROLLER BOARD

#### General Description

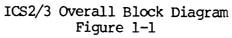

The controller board can be logically divided into two functional areas:

- The Z8001 microprocessor, Z8001 support logic, memory storage, microprocessor-bus and associated input/output devices

- The Inter-Bus Controller (IBC)

Memory storage for microprocessor programs and data buffering is as follows. The ICS2 has a 2K x 16-bit word PROM, and up to 256K bytes (128K x 16-bit words) of dynamic RAM.

The ICS3 has a 8K x 16-bit word EPROM, and up to 1024K bytes (512K x 16-bit words) of dynamic RAM. The microprocessor communicates with its memory and input/output (I/O) devices over the 16-bit microprocessor bus (uBus).

The I/O devices residing on the uBus include a general purpose Counter-Timer Circuit (CTC), the standard Prime I/O interface logic components, the IBC, and for the ICS3 only, a Serial Communications Controller (SCC).

The IBC is a microprogrammed device whose primary purpose is to move data between three buses:

- The uBus

- The LAC bus

- The Prime I/O bus

Figure 1-2 is a block diagram showing the interconnection of the various components of the controller board.

1-5

#### Microprocessor and Support Logic

The 16-bit Zilog Z8001 microprocessor is the main control element of the ICS2/3. Support logic for the Z8001 microprocessor consists of the following:

- Clock driver circuit

- Reset control logic

- State and address decode logic

- Bus buffers

- Microprocessor status register

<u>Clock Driver Circuit</u>: This circuit is necessary to ensure that the stringent timing and level specifications for the Z8001 clock input are met. Clock speeds are 8Mhz for the ICS3 and 4Mhz for the ICS2.

<u>Reset Control Logic</u>: The reset control logic has two functions: it synchronizes the asynchronous reset inputs to the microprocessor clock, and it also ensures the proper resetting of the microprocessor.

State and Address Decode Logic: The state decode logic decodes the four state lines (STATEO-3) from the microprocessor into one of 16 possible microprocessor state output signals. These output states indicate what cycle type is currently being executed. The address decode logic comprises the address latch, segment number latch, and segment number decoder. The output from the segment number latch (LSEGNO-6) is decoded and used in conjunction with the output from the address latch (MADOO-15) to select memory and peripheral devices.

Bus Buffers: These are a necessary requirement due to the limited drive current of the Z8001 microprocessor.

<u>Microprocessor Status Register</u>: The microprocessor status register is a 16-bit read-only register residing on the uBus. The data input consists of a number of status signals, routed from various areas of the controller board logic; these signals provide essential state information to the microprocessor.

#### Microprocessor Bus (uBus)

The uBus is comprised of 16 bi-directional lines designated ZAD00-15, which connect the microprocessor to its memory and other associated peripherals. Address and data information are multiplexed on the uBus. In addition to the 16 multiplexed address lines, the uBus includes seven address lines for the segment number (SEGN0-6). The segment number address lines increase the byte addressable memory from 64K bytes to a possible 8M bytes.

#### ICS3 Controller Board LED Lights

The ICS3 controller board is fitted with four LED indicator lights. These will flash or remain on when the following events occur:

- LED 1 (Flash) Warning LAC card cage power failure

- LED 2 (Flash) Warning Single-bit memory parity error detected

- LED 3 (On) Fatal WCS parity error detected

- LED 4 (Flash) RUN light -- when VERIFY is completed and the operating system is functioning correctly

All LEDs flash when multiple bit errors are detected.

#### Memory

Microprocessor PROM: The ICS2 has 4K bytes of PROM, and the ICS3 has 16K bytes of EPROM, both containing

- Initialization routines

- Bootstrap routines

- Self verification routines

<u>Microprocessor RAM</u>: On the ICS2, the microprocessor RAM consists of up to 256K bytes (128 x 16-bit words) of dynamic memory, with even parity checking on each byte. On the ICS3, the RAM consists of up to 1024K bytes (512 x 16-bit words) of dynamic memory with Error Checking and Correction (ECC) logic, capable of detecting multiple-bit errors and correcting single-bit errors. A minimum of 256K of memory is required to run any of the synchronous support options on the ICS2/3.

#### Input/Output Devices

<u>Counter-timer Circuit</u>: Three independent sections comprise the counter-timer circuit. All sections are implemented using a Zilog Z80A-CTC chip and the microprocessor clock ZCLK+. The sections function as follows:

- Section 0 is an independently programmable timer used by the microprocessor for general timing purposes. It generates non-vectored interrupts to the microprocessor.

- Section 1 is similar to Section 0, but with the added capability of using timeouts on CTC section 0 to count down its time-constant register. This enables cascading to create longer timeout intervals.

- Section 2 is a uniquely configured counter or timer section that, on timeout, generates segment traps to the microprocessor. Section 2 has the ability to use either the clock ZCLK+ or stack references to count down its time-constant register. The configuration of Section 2 enables hardware single-stepping to be implemented. Single stepping is used in diagnostic routines.

Standard I/O Interface Logic: The standard Prime I/O interface is composed of three logic units:

- The OTA FIFO is a 20-bit x 16 word, first-in-first-out memory used to store and buffer OTA instructions received by the ICS2 from the Prime. Because the rate at which the host CPU issues OTA instructions is potentially faster than the microprocessor handling rate, some form of queuing is required.

- The INA register is a 16-bit register written-to by the microprocessor and read by any INA instruction sent from the host CPU (Prime). A non-vectored interrupt informs the microprocessor that data has been read by the host CPU.

- The direct-memory-access interface logic (which incorporates the interrupt interface logic) enables the microprocessor to set up and request direct memory cycles on the Prime I/O bus. The microprocessor initiates DMX cycles by configuring the address, mode, and data registers as appropriate, and then setting up the DMX request logic.

Interrupt interface logic is the mechanism for setting up and requesting Prime vectored interrupts.

<u>Serial Communication Controller (SCC)</u>: A dual-channel Z8530-SCC is used on the ICS3 for the main purpose of supporting RASBUS. The primary task of the SCC is to perform serial-to-parallel conversion for the two communication channels. The two channels are used as follows:

- Channel A is used as a general purpose link for direct communication to the Z8001 using an RS232 interface provided on the ICS3.

- Channel B is dedicated to the sole purpose of supporting RASBUS.

<u>Inter-Bus Controller (IBC)</u>: The IBC is a specialized, high-speed microcode programmed device whose primary task is to control the flow of data between the three buses under its influence:

- The 16-bit microprocessor bus (uBus)

- The 8-bit LAC bus

- The Prime I/O bus

The IBC also allows a reduction in the logic that would otherwise be required on the LACs.

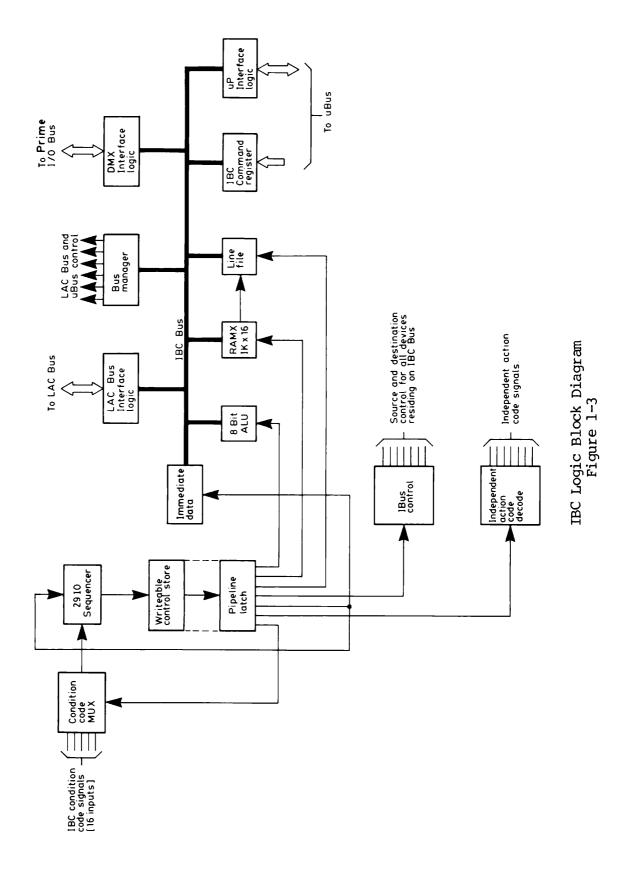

The interconnection of the IBC is shown in Figure 1-3 and includes the listed logic components, which are described in the following pages.

- Sequencer

- Writeable Control Store and Pipeline Latch

- Independent Action Code (IAC) Decoder

- IBC Bus Control

- ALU (Arithmetic Logic Unit)

- Line File

- RAMX

- Bus Manager

- LAC Bus Interface Logic

- Microprocessor Bus Interface Logic

- DMX Interface Logic

- IBC Command Register

Sequencer: The 12-bit sequencer provides an address into the writeable control store. A 4-bit microcode field on the input of the sequencer selects one of 16 possible sequencer instructions.

The execution of most of the sequencer instructions depends upon the output from the condition code multiplexer logic. This output is a 4-bit microcode field that allows for the selection of one of 16 possible condition codes. These condition codes are states that exist in the IBC and can be tested by the microcode.

The sequencer can be stopped, started, and single-stepped by the microprocessor; this capability provides a powerful debugging feature for the hardware and software components of the ICS2/3. This facility is available only for Prime internal development personnel, and consequently, is not visible to users.

Writeable Control Store and Pipeline Latch: In the ICS2, the Writeable Control Store (WCS) is a 56-bit wide by 1K deep memory that stores the control code (microcode) for the IBC. In the ICS3, the WCS is 64 bits wide by 4K deep, and contains parity logic. The 56/64-bit output word is latched from the WCS into the pipeline latch on every IBC cycle; from there, it is divided into microcode fields that are used for control purposes throughout the IBC. There are seven microcode fields output from the pipeline:

- Sequencer operation field (Sequencer)

- ALU control field (ALU)

- IBC source and destination control field (IBC Bus Control)

- Line file index field (Line File)

- Independent Action Code (IAC) select field (Independent Action Code Decoder)

- Condition code select field (Condition Code Multiplexer)

- Next address/immediate data field (IBC Bus)

Independent Action Code Decoder: This logic decodes the microcode field from the WCS into IAC signals. These code signals are used to activate control signals in the IBC.

IBC Bus Control: The 16-bit IBC bus interconnects various data sources and destinations throughout the IBC. The IBC bus control specifies, in microcode, the source and destination devices for the movement of any data on the IBC bus.

Arithmetic Logic Unit: The IBC ALU is a general purpose 8-bit ALU residing on the IBC bus. The ALU is capable of performing both arithmetic and logical functions under the control of the microcode input from the pipeline latch.

Line File: The line file is a 2K (ICS2), or 4K (ICS3), by 16-bit RAM residing on the IBC bus. Its function is to store single line DMA pointers and state information. Each line on the LAC bus is allocated a maximum of four blocks of storage, within the line file, to accommodate a maximum of four possible DMA or data movement channels associated with each line.

RAMX: The RAMX is a lK (ICS2), or 4K (ICS3), x 16-bit high-speed RAM residing on the IBC bus. On the ICS2, the RAM is divided into four 256 x 16-bit sections, named RAMO, through RAM3. On the ICS3, the RAM is divided into sixteen  $256 \times 16$ -bit sections, named RAMO through RAM15.

RAMO is used to store mapping information that enables physical LAC bus addresses to be mapped to logical addresses used by the line file. RAMO also supplies the two control bits for determining the line-file block size in the line-file address multiplexing logic.

RAM1, 2 and 3 are used for protocol-specific storage.

RAM4 through RAM15 are available for general purpose storage.

Bus Manager: The bus manager is a small-state machine that incorporates configured PROMs and registers, which generate timing signals for the LAC bus and the uBus. The bus manager is initiated under microcode control, and supports three LAC bus cycle types (read, wait, interrupt acknowledge) and two uBus cycle types (read, write). The ICS3 bus manager consists of Programmable Logic Arrays (PLAs or PALs) with registers, which replace the PROMS and registers of the ICS2.

LAC Bus Interface Logic: The LAC bus interface logic consists of address and data registers, which are used in conjunction with the bus manager, to execute LAC bus read, write, and interrupt acknowledge cycles. The interface logic incorporates line drivers and receivers to interface via the 26-foot controller board to buffer board cable.

Microprocessor Bus Interface Logic: The microprocessor bus interface logic consists of four 16-bit registers, an 8-bit register, a tri-state driver for the four microprocessor state lines, and the microprocessor vectored-interrupt request flip-flop. The logic has two functions:

- To transfer data to and from the Z8001

- To initiate vectored interrupts to the Z8001

DMX Interface Logic: The DMX interface logic comprises address, data, and mode registers, which are configured and read by the IBC when executing I/O bus DMX cycles. The interface logic also includes an IBC DMX request bid flip-flop, an IBC DMX request flip-flop, and an IBC DMX end-of-range flip-flop. This logic is capable of executing the following transfers on the Prime I/O bus:

- DMA -- Direct Memory Access

- DMC -- Direct Memory Control

- DMT Direct Memory Transfers

- DMQ -- Direct Memory Queue

The DMX interface logic supports an 18-bit DMX address.

IBC Command Register: The IBC command register is a 16-bit register into which is written 16 bits of command data sent from the Z8001 to the IBC. This register is an IBC read-only register.

#### LAC CARD CAGE ASSEMBLY

The LAC card cage is available in three sizes to accommodate two LAC sizes.

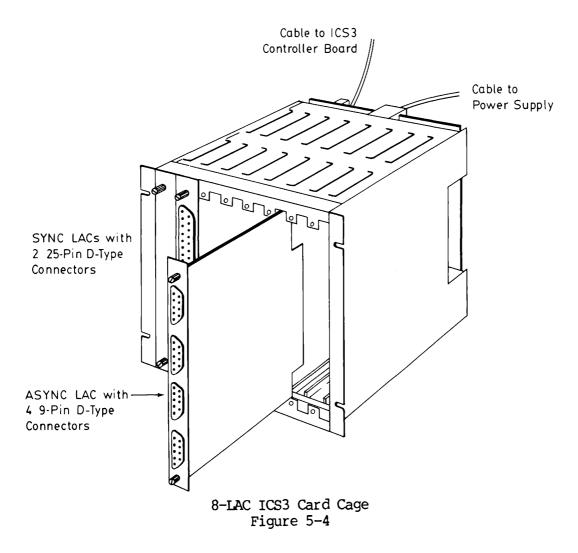

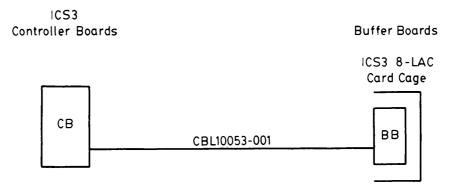

#### 8-LAC ICS3 Card Cage

This card cage houses the smaller (6.5 by 5 inches) ICS3 LACs used on small Prime systems requiring up to eight LACs. The card cage contains its own backplane and buffer board, but is not fitted with a power supply. A separate cable provides power from the CPU power supply. (Refer to Figure 5-4, 8-LAC ICS3 Card Cage, in Chapter 5, CONFIGURATION.)

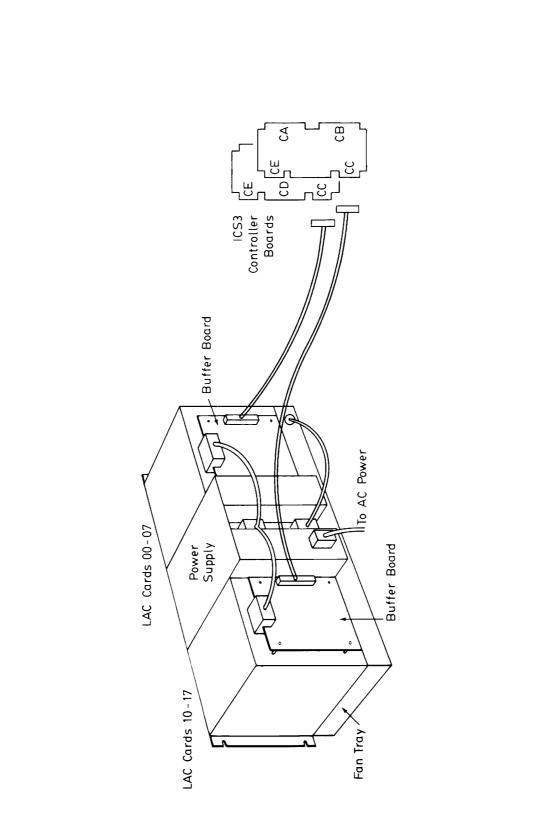

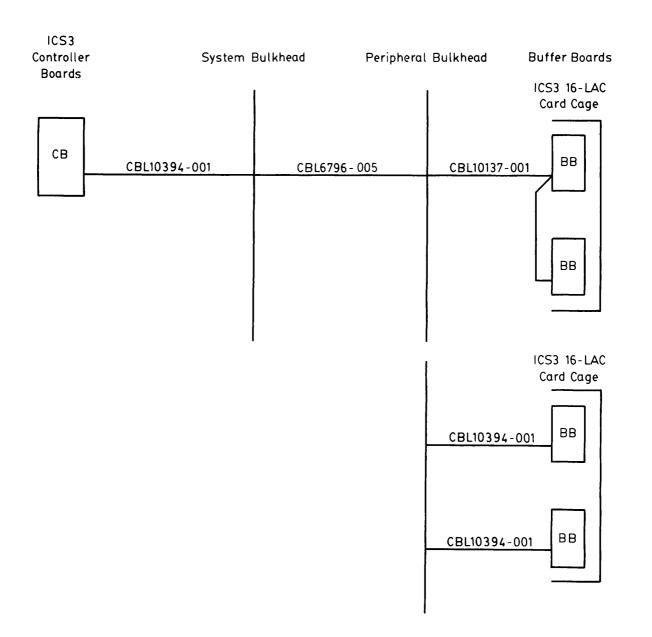

#### 16-LAC ICS3 Card Cage

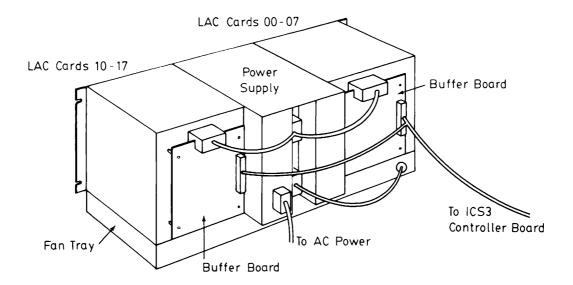

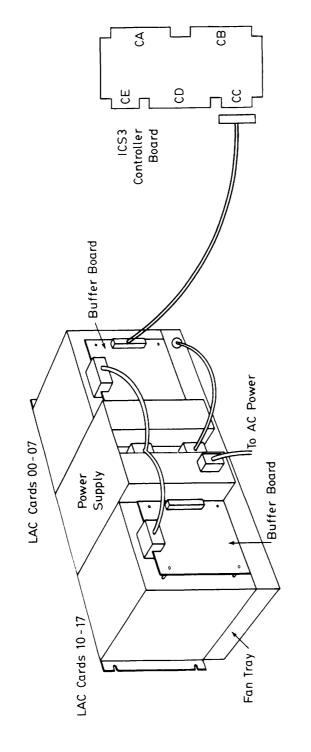

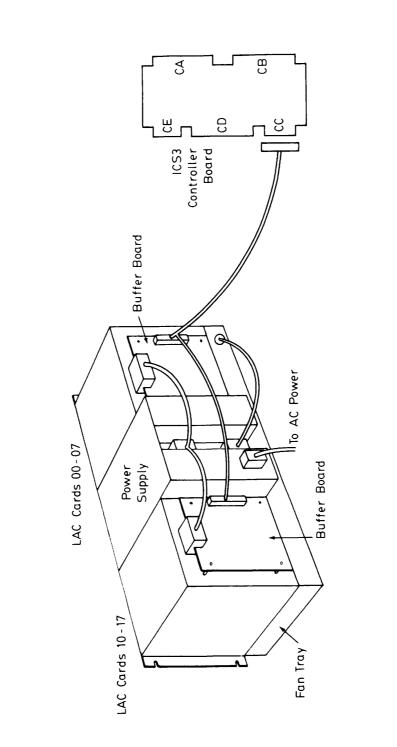

This card cage houses (in two groups of eight) up to sixteen of the smaller (6.5 by 5 inches) ICS3 LACs. Each group of eight LACs has its own backplane and buffer board. One power supply, fitted between the two groups of eight LACs, provides power for all sixteen LACs. (Refer to Figure 5-5, 16-LAC ICS3 Card Cage, in Chapter 5, CONFIGURATION.)

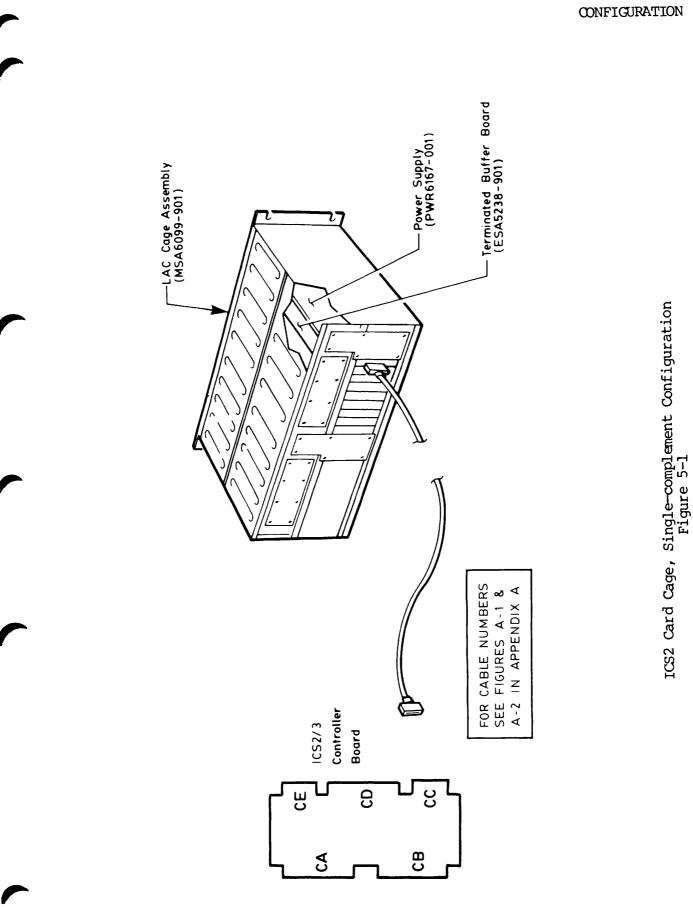

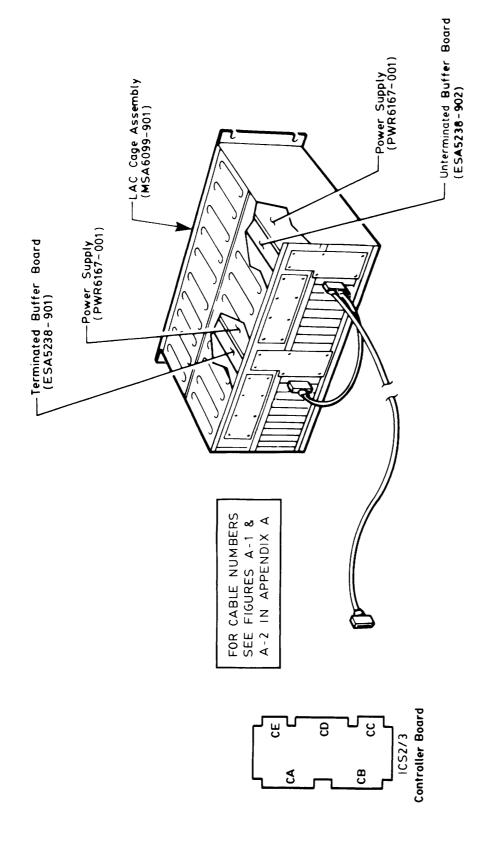

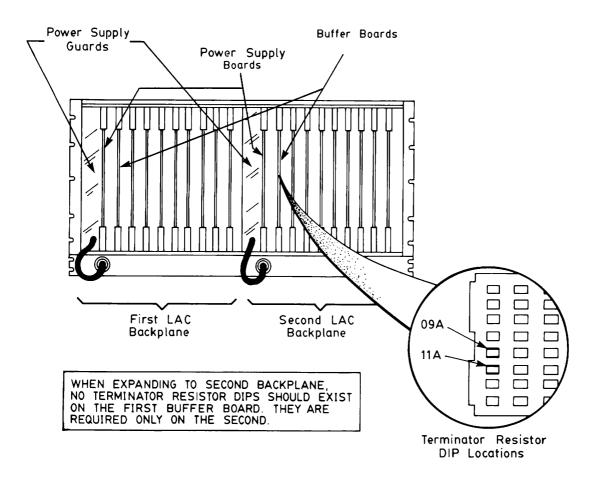

#### ICS2 Card Cage

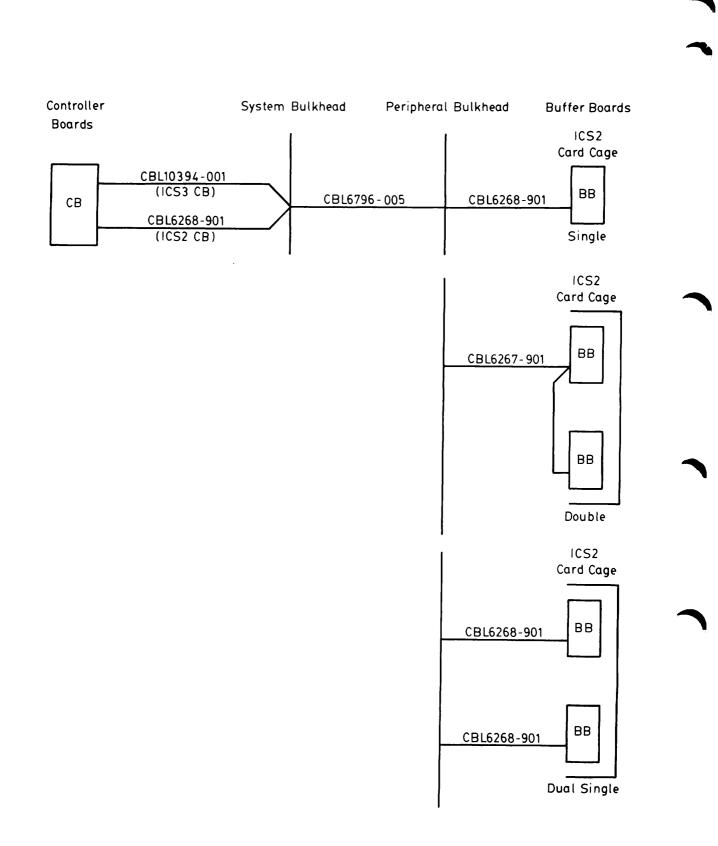

This card cage houses the larger (10 by 8 inches) ICS2 LACs. It can contain up to sixteen LACs, and a backplane, buffer board, and power supply for each group of eight LACs. (Refer to Figure 5-8 and Figure 5-10 in Chapter 5, CONFIGURATION.)

#### Buffer Board

The buffer board comes in two sizes; 10 by 8 inches for the ICS2 cage, and 6.5 by 5 inches for the ICS3 cages. The ICS2 buffer board plugs into the slot on the right of each power supply board in the ICS2 LAC cage. On ICS3 LAC cages, the ICS3 buffer board mounts on the back of, and parallel to, the backplane. The primary function of the buffer board is to provide an electrical interface between the 50-wire cable from the controller board and the LAC bus. The LAC bus resides on the backplane of the LAC card cage assembly.

A green LED, located on the front of the ICS2 buffer board, indicates that power is available on the LAC bus backplane.

Additional functions performed by the buffer board are accomplished by the following logic circuits:

- Cable interface

- LAC bus interface

- Parity logic

- Interrupt acknowledge logic

<u>Cable Interface</u>: Interfacing of the 50-wire cable, which connects the controller board to the buffer board, is achieved by using open collector bus transceivers. The cable signal wires are terminated on both ends of the cable.

LAC Bus Interface: The buffer board interface to the backplane is relatively simple, due to the short length of the LAC bus backplane. The majority of the LAC bus control signals are driven directly from the receive side of the bus transceivers. Parity Logic: The buffer board parity generation/checking logic is used to generate and check parity on the data and address information transmitted over the controller board to buffer board cable. Furthermore, the parity logic checks the cable transceivers and the LAC bus transceivers because no parity checking is carried out on the LAC bus backplane or within the LACs.

Under normal operation, LAC bus read cycles to a nonexistent slot or backplane do not generate a parity error.

Interrupt Acknowledge Logic: The buffer board interrupt acknowledge logic is used to prioritize the LAC bus interrupt requests and to select the highest priority LAC during LAC bus interrupt acknowledge cycles. The buffer board receives separate interrupt request lines from each LAC.

Because two buffer boards and, in turn, two LAC backplanes can be connected to one controller board, additional logic has been incorporated to differentiate the buffer board that should receive the data cycle. A signal, generated in the buffer board, is used to make the determination. As a result, during interrupt acknowledge cycles, the buffer board knows whether or not the cycle is for a slot in its backplane.

In addition to prioritizing LAC bus interrupt requests, the buffer board also modifies the interrupt vector obtained from the LACs during interrupt acknowledge cycles.

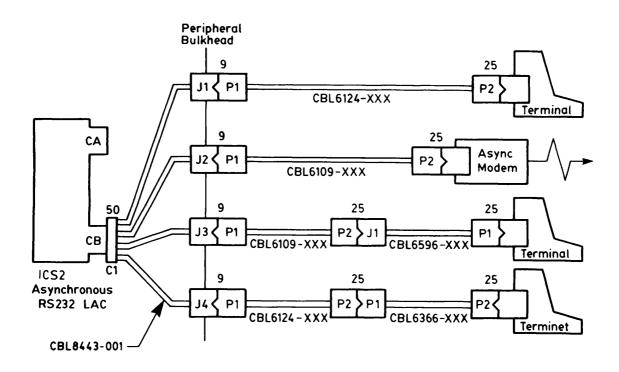

#### Asynchronous RS232 LAC

There are two basic types and sizes of asynchronous LACs. The ICS2 LAC type (10 by 8 inches) uses Zilog's SIO (Serial Input/Output) controller, while the ICS3 LAC type (6.5 by 5 inches) uses Zilog's SCC (Serial Communications Controller). The ICS3 controller board will support both SIO-fitted and SCC-fitted asynchronous LACs. However the ICS2 controller board only supports SIO-fitted asynchronous LACs.

The asynchronous RS232 LAC sends and receives serial streams of data to and from the Data Terminal Equipment (DTE). In asynchronous mode, characters are delimited by start and stop bits that help to synchronize character bit timing. The following logic circuits comprise the asynchronous RS232 LAC:

- Standard LAC Bus Interface Logic

- Baud Rate Generator

- Timing Generation Logic: SIO (Zilog Serial I/O controller) in the ICS2, and SCC (Zilog Serial Communications Controller) in the ICS3

- SIO/SCCs and Support Logic

- Loopback Control Logic

- Electronic Industries Association (EIA) Interface Circuit

Standard LAC Bus Interface Logic: The asynchronous RS232 LAC uses standard LAC bus interface logic. Because the LAC bus has a multiplexed address and data path, the address is latched on each LAC bus cycle and the bidirectional data is buffered by using tri-state devices.

Each LAC is assigned an 8-bit ID, which is addressed during a read cycle.

<u>Baud Rate Generators</u>: Two baud-rate generators provide the four baud-rate clocks for the communication lines on the asynchronous RS232 LAC. A four-bit code sent by the IBC configures each clock to the desired speed.

The four baud-rate clock outputs are connected directly to the four serial input/output communication lines on the LAC. The speeds for these lines are described in the <u>System Administrator's Guide</u>, Rev. 20, under the ICS JUMPER directive. (The ASYNC JUMPER directive replaces the ICS JUMPER directive; both are currently supported.)

#### Note

The transmit and receive baud-rate clocks for each communications line are currently constrained to run at the same speed.

SCC Timing Generation Logic: The ICS3 asynchronous LAC uses the Zilog Serial Communications Controller (SCC) chip instead of the Zilog Serial Input/Output (SIO) chip used in the ICS2 asynchronous LAC. This chip performs serial-to-parallel and parallel-to-serial conversion. It enables the SCC to read and write data and interrupt acknowledge cycles. SIO Timing Generation Logic: The SIO timing generation logic forms the control signals that the SIO requires for read, write, and interrupt acknowledge cycles.

SIOs and Support Logic: Each asynchronous RS232 LAC is fitted with two dual-channel SIO devices. These provide the primary function of serial-to-parallel and parallel-to-serial conversion for the four communication lines. Additional SIO functions include protocol handling, data set status, data set control line handling, and interrupt vector generation.

#### Note

The SIO devices on the asynchronous RS232 LAC are the only generators of LAC bus interrupt requests.

The SIO support logic basically consists of address decode logic, which is used to select the appropriate SIO (Zilog).

Loopback Control Logic: Each of the asynchronous RS232 LAC's four communication lines has a data loopback capability. Primarily, the data loopback capability loops the transmit data back through receive data on a particular communication line. This loopback gives the ICS2/3 the ability to verify the correct operation of a LAC by transmitting data to the SIO/SCC chip and verifying that the data returns intact via the receiving line. This is a software-enabled hardware loopback.

EIA Interface Circuit: The EIA (Electronics Industries Association) interface circuit provides signal level conversion between TTL signals and the EIA signals. This signal level conversion is required for interfacing to the RS232/V24 configured equipment. Each communication line on the asynchronous RS232 LAC transmits and receives three EIA signals. Transmitted EIA signals are

- Transmit data

- Request to send (RTS is held high)

- Data terminal ready (controlled by the PRIMOS® operating system)

Received EIA signals are

- Receive data

- Data carrier detect

- Clear to send

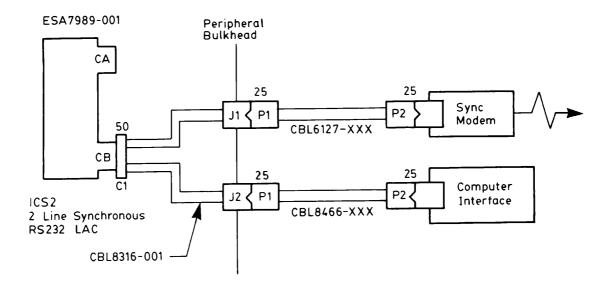

#### Synchronous LAC

There are two sizes of synchronous LACs: 10 by 8 inches, for the ICS2 LAC card cage, and 6.5 by 5 inches, for the ICS3 LAC card cages. The ICS3 controller board supports both sizes, but the ICS2 controller board supports only the ICS2 size.

The synchronous and asynchronous LACs are very similar. Their basic differences are

- The synchronous LAC supports two lines compared to the four-line support of the asynchronous LAC

- The synchronous LAC supports four dataset control signals (modem speed select, DIR, RTS, spare) and four dataset status signals (CTS, DCD, DSR, RI) for each line. The asynchronous LAC supports only two dataset control signals and two dataset status signals per line

- The synchronous LAC has no programmable loopback capability

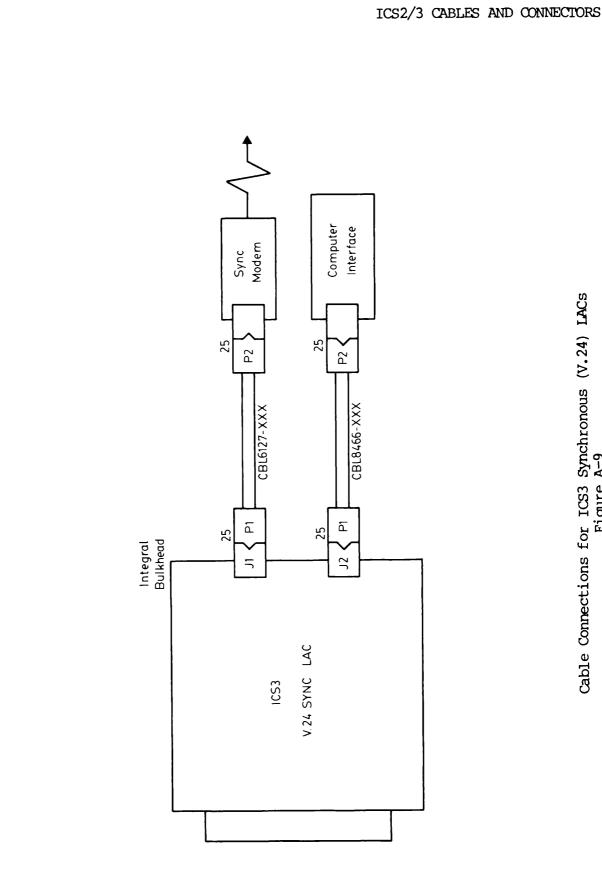

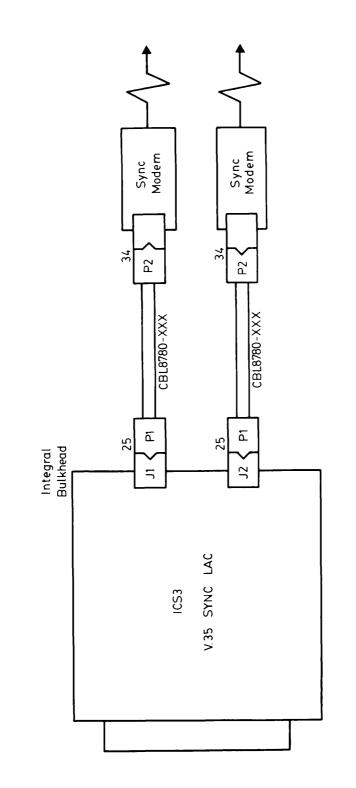

- The synchronous LAC is available in two versions: V.24 and V.35. The V.24 LAC is intended for applications that support line speeds to a maximum of 19,200 bps, whereas the V.35 LAC is required for the higher speed operations that range from 19.2 to 64 Kbps. The V.24 and V.35 LACs require different cabling to the Prime bulkhead and from the Prime bulkhead to the customer equipment. (See Appendix A.) The ICS3 LACs have integral bulkheading.

- The synchronous LAC uses the Zilog SCC (Serial Communication Controller), while the asynchronous LAC uses either the SCC (for use with ICS3 only), or the SIO Serial Input/Output for use with ICS2 or ICS3 controller boards.

#### Power Supply Card

The power supply, or power supply card, provides the buffer board(s) and the LACs with regulated voltages. The power supplies can be internally configured for the various voltage/frequency requirements of different countries.

#### LAC Bus

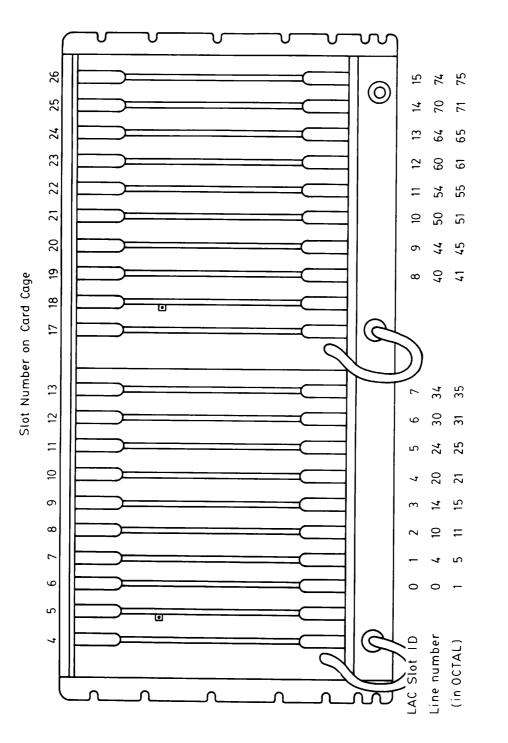

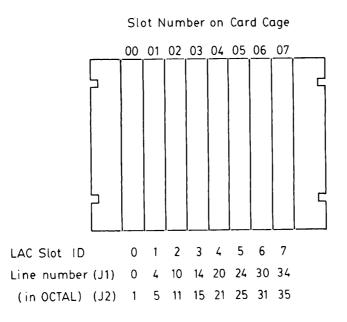

The LAC bus consists of a synchronous, tri-state, 8-bit bus incorporating a multiplexed address and data path. In addition, the LAC bus includes

- Four slot select bits, which interact with the hardwired slot numbers on the LAC bus backplane and are used for LAC and LAC bus backplane selection

- Two line select bits, which are used for selection of LAC communication lines 1 through 4

- Various control signals

Three types of LAC bus cycles are supported: read, write, and vectored interrupt acknowledge.

#### EXTERNAL INTERFACES AND CABLING

The ICS2/3 communicates with external equipment via the following interface connectors:

- The Electronics Industries Association (EIA) RS232 interface or the compatible International Telegraph and Telephone Consultative Committee (CCITT) Recommendation V.24

- The CCITT Recommendation V.35

- AT&T's Dataphone Digital Service (DDS)

On an ICS2 LAC, one cable connects a LAC to the Prime bulkhead, and another cable connects the bulkhead to external equipment. On an ICS3 LAC, the cable to the external equipment is attached directly to the integral bulkhead on the edge of the LAC.

#### EIA RS232/CCITT V.24

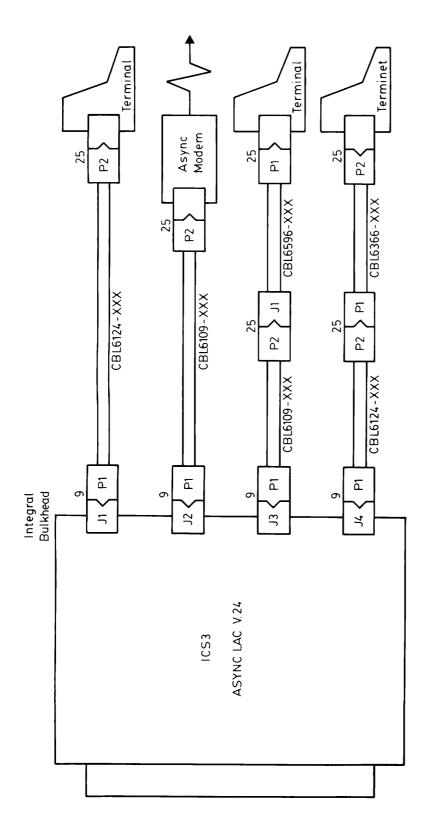

Two different cable configurations are required for RS232/V.24 connection.

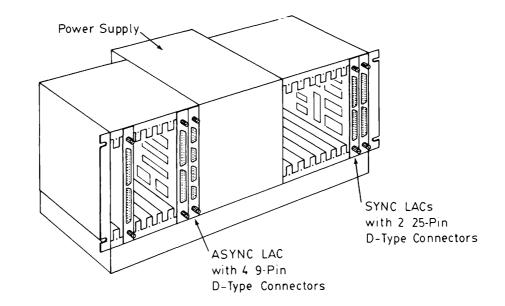

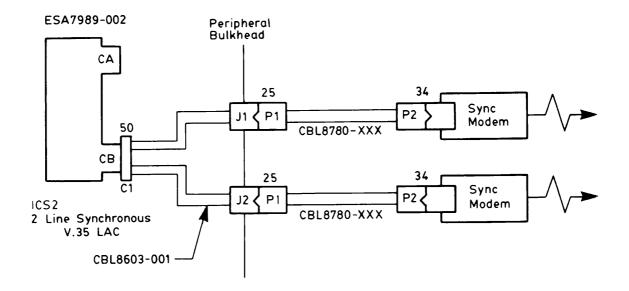

The ICS2 LACs require a cable from the LAC to a peripheral bulkhead. The LAC connection is via a 50-pin connector. The synchronous cable terminates (at the bulkhead) in two 25-pin D-type connectors, while the asynchronous cable terminates (at the bulkhead) in four 9-pin D-type connectors. Further cables then connect from the bulkhead to external V.24 or V.35 equipment. Cable numbers and pin assignments are listed in Appendix A, ICS2/3 CABLES AND CONNECTORS.

The ICS3 LACs have integral bulkheading. This means that the asynchronous LACs have four 9-pin D-type connectors for direct connection of cables to terminals, printers, or modems. The synchronous LACs (V.24 and V.35), have two 25-pin D-type connectors, for direct connection of cables to modems.

#### CCITT V.35/DDS

The CCITT Recommendation V.35 interface is for connection to wideband modems using data transmission rates of 19.2 - 64 Kbps.

The pin assignment of the V.35 cables and connectors is given in Appendix A.

# ENVIRONMENTAL SPECIFICATIONS

Table 1-1 shows the environmental specifications for the ICS2/3.

| Operational Temperature:    | 59-90 degrees F<br>(15-32 degrees C)                                             |

|-----------------------------|----------------------------------------------------------------------------------|

| Operational Humidity:       | 30%-80% non-condensing                                                           |

| Storage Temperature:        | -40 to +140 degrees F<br>(-40 to +60 degrees C)                                  |

| Storage Relative Humidity:  |                                                                                  |

| Vibration: Operational:     | 0.25g; 5 to 200 Hz<br>Horizontal and Vertical                                    |

| Vibration: Non-operational: | Vertical; 0.33g<br>5 to 200 Hz Random<br>Horizontal; 0.68g<br>5 to 200 Hz Random |

| Altitude Operational:       | 10,000 feet                                                                      |

| Altitude Non-operational:   | 40,000 feet                                                                      |

| Acoustic Noise:             | 43 db at 125 Hz<br>34 db at 250 Hz<br>34 db at 500 Hz                            |

| AC Voltage:                 | 104-127 VRMS<br>208-254 VRMS                                                     |

| AC Frequency:               | 60 +/- 1 Hz, or<br>50 +/- 1 Hz                                                   |

|                             |                                                                                  |

Table 1-1 Environmental Specifications

# 2 ICS2/3 Software

#### INTRODUCTION

The ICS2/3 software consists of the following:

- ICS2/3-to-PRIMOS communications software

- ICS2/3 operating system

- IBC microcode

- User protocol-specific modules

The software supports HDLC and BSC framing for the PRIMENET/X.25 communications software, BSC-based RJE protocols for IBM 2780/3780 and HASP, SDLC for PRIME/SNATM software, and asynchronous communications.

The associated software-supported protocols are as follows:

- FDX (Full duplex) with High-level Data Link Control (HDLC) using CCITT X.25 protocols and PRIMENET

- HDX (Half duplex) with IBM's binary synchronous communications protocol (BSC) for IBM 2780/3780/HASP RJE support

- FDX and HDX with BSC framing using X.25 protocols

- SDLC for PRIME/SNA communications with SNA hosts

- ASYNC for terminals, printers, and switched-line modems

2-1

Starting with Rev. 20.1, the ICS3 with 512K byte memory (or larger) can handle any combination of the allowable protocols (ASYNC, HDLC, SDLC, BSCRJE, and BSCX25). The ICS3 with 256K byte memory can handle every protocol combination except the two largest ones, ASYNC\_SDLC\_HDLC\_BSCRJE\_BSCX25 and SDLC\_BSCX25\_BSC\_RJE. The ICS2 limits the combination of protocols (see Chapter 5) to the following:

- Any one protocol

- ASYNC, HDLC, and SDLC

- HDLC, SDLC, BSC-framed X.25 (BSCX25), and BSC RJE (BSCRJE)

- Non-reverse-flow-control ASYNC with BSC (BSCRJE and/or BSCX25) (Equivalent to pre-Rev. 19.4 functionality for the ICS2 ASYNC.)

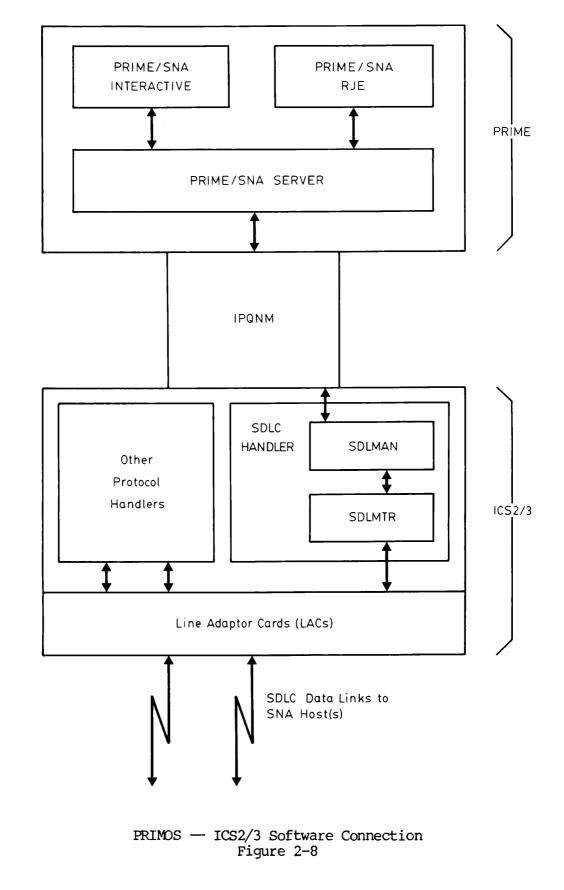

#### ICS2/3 - PRIMOS SOFTWARE

The software interface between the ICS2/3 processes and PRIMOS processes consists of a message protocol using the Interprocess Queuing and Notification Mechanism (IPQNM) to transfer the data, buffers, and commands. The IPQNM consists of a set of routines that run with the calling process and supporting processes, and use logical connection techniques to communicate with each other.

IPQNM uses high and low priority queues to send information over its logical connections. At least one queue must be specified by a process requesting a logical connection, in which case it is designated as a normal or low priority queue. If there are two queues required, the second is designated as a high priority queue.

- The low priority queue is a default or normal priority queue. Information sent over the logical connection using this queue is received by the other process in the sequence it was sent.

- The high priority queue can be specified in either direction for a logical connection. Any information sent on the high priority queue, by a calling process, is given to the other process before any information still remaining on the low priority queue.

The message protocol consists of a set of control blocks and code words. PRIMOS sends multi-word control blocks to the ICS2/3 to define line configuration and to control synchronous communication lines. The line configuration informs the ICS2/3 about line characteristics such as protocol, data set order, parity selection, number of bits per character, and special characters to be detected. PRIMOS controls the synchronous communication lines by sending information about synchronous I/O operation for the specified communication line, such as transmit/receive and data set control. The IPQNM creates the logical connections between communicating processes from information received from the calling process. A maximum of 64 logical connections can be initiated; however, logical connections 0 and 1 are used only for the following specific functions:

- Logical connection 0

- Initializes the ICS2/3's IPQNM data structure upon request from the calling process

- Deletes or initializes a logical connection between an ICS2 process and a PRIMOS process

- Notifies the ICS2/3 process, including logical connection 1, with the event code placed on the event queue

- Logical connection 1

- Returns transmit buffers to the PRIMOS Buffer Server process

- Obtains receive buffers from the PRIMOS Buffer Server process

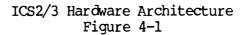

#### PRIMENET/X.25 Support Software

The ICS2/3 PRIMENET/X.25 software enables PRIMOS to configure lines on the ICS2/3 to support HDLC and BSC-framed X.25 protocols. PRIMENET/X.25 lines can be full or half duplex on the ICS3, and full duplex only on the ICS2.

Half duplex lines support a Prime-specified BSC protocol used solely for connection to other Prime machines. This is usually referred to as Half Duplex PRIMENET and is supported on the ICS3 (only) at Rev. 21.0.

Using PRIMENET/X.25 enables inter-machine communication via any Packet Switched Data Network (PSDN) that supports the X.25 protocol or via any point-to-point/Prime-to-Prime link that uses synchronous lines.

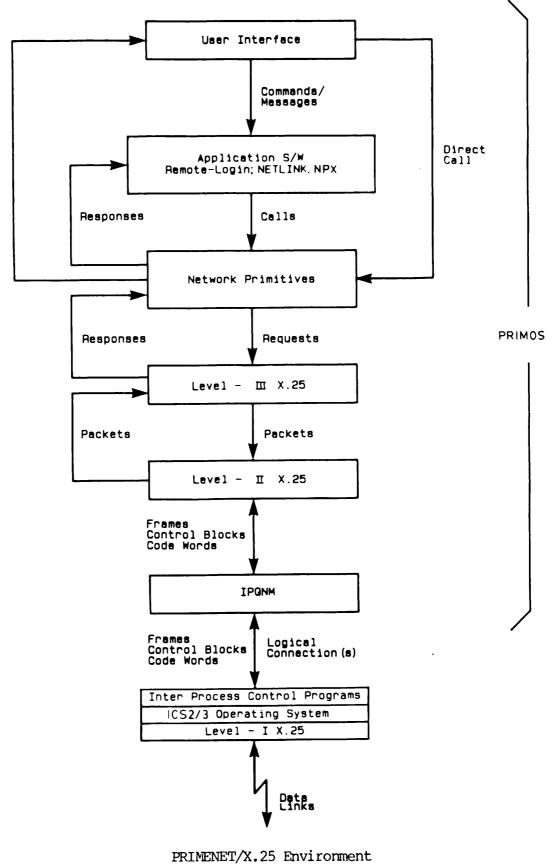

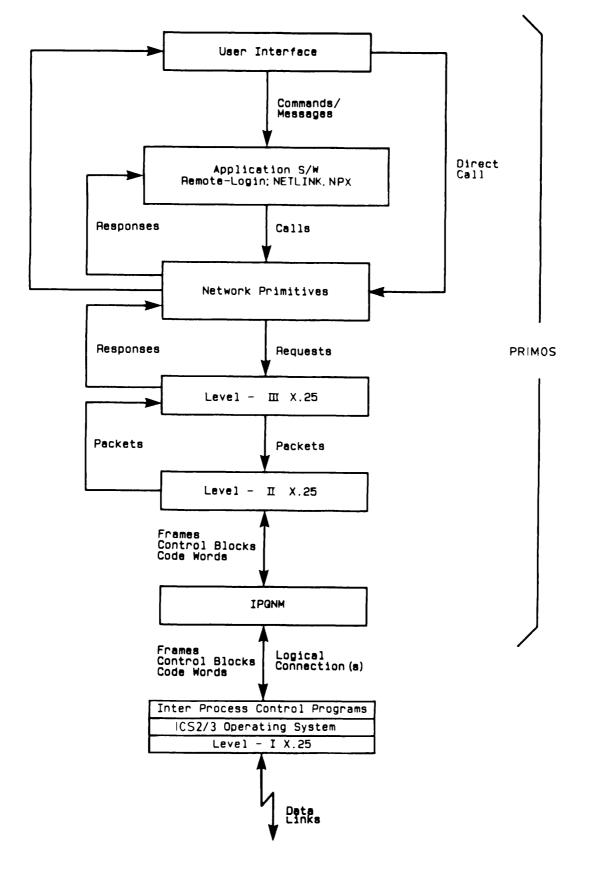

PRIMENET/X.25 follows a layered construction with Level III (packet/ network-level) and Level II (framed/link-level) software residing in the Prime machine, and Level I (physical-level) residing in the ICS2/3 as shown in Figure 2-1. Some of the sequence-number handling of Level II is performed in the ICS2/3.

The ICS2/3 uses the IPQNM to communicate with PRIMOS over high and low priority queues. Each X.25 line has one logical connection from the ICS2/3 to the Prime, and it shares two common free-pool buffers on the host.

All control messages, X.25 unnumbered frames, and X.25 supervisory frames from PRIMOS are put on the high priority queue, and all X.25 information frames from PRIMOS are put on the low priority queue. All control messages from the ICS2/3 are put on the high priority queue, and all X.25 frames from the ICS2/3 are put on the low priority queue.

Users can invoke PRIMENET/X.25 in two ways. These are

- Through Prime-supplied applications software, such as Remote File Access and remote login, which provide a user-level interface. These packages invoke the network primitives from within PRIMOS and provide a more transparent (friendly) interface to the user.

- By direct call to the network primitives, provided by the user protocol-specific interprocess communication facility. This enables the users to write protocol-specific software modules to customize communication interfaces.

Figure 2-1 shows the PRIMOS-to-ICS2/3 software interconnection.

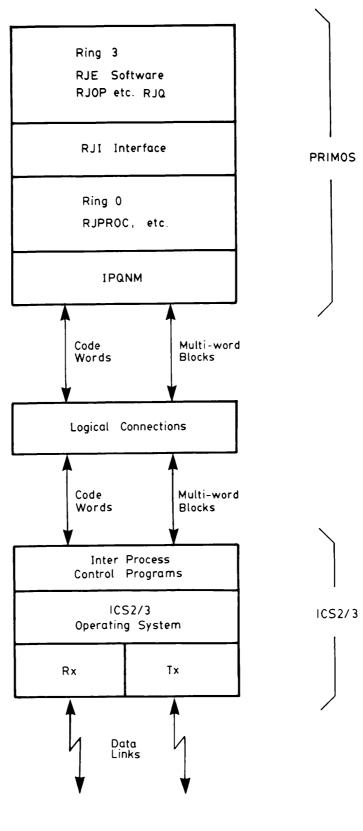

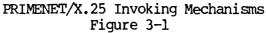

#### RJE Support Software

Remote Job Entry (RJE) emulators allow Prime computers to emulate various RJE terminals/workstations, thus enabling communications between Prime and other host computers. Communications are normally accomplished by the transfer of files from one computer system to another via synchronous links in accordance with the specific RJE data link control protocol.

Prime RJE emulators support the following RJE stations via the ICS2/3:

- 2780 (IBM)

- 3780 (IBM)

- HASP (IBM)

SNA RJE is supported in that the ICS2/3 supports SDLC; however, no support specific to SNA RJE is performed in the ICS2/3.

The ICS2/3 acts as an interface between the Prime systems and RJE hosts connected via synchronous communication links. The ICS2/3 receives data over the communication lines, packs the data in the form of blocks (after doing preliminary checks), and sends the data block to the Prime system. In a similar way, it receives the data and control information from PRIMOS and then transmits it to the specified communication line.

The RJE support software on the ICS2/3 handles the data set monitoring and control for all synchronous communication lines connected to it. ICS2/3 — PRIMOS communication is performed via IPQNM, using one logical connection per line. The RJE support software is responsible for the following functions, which are performed by the ICS2/3 and coordinated by Ring 0 process in PRIMOS:

- Reception and transmission of data over the lines

- Communicating with PRIMOS via IPQNM

- Detecting special character sequences

- Sending line status to the Prime host

- Cyclic redundancy check (CRC) generation and checking

- Detecting loss of synchronization

- Handling dataset control and responses

The RJE environment showing the software functional interconnection is illustrated in Figure 2-2.

RJE Environment Figure 2-2

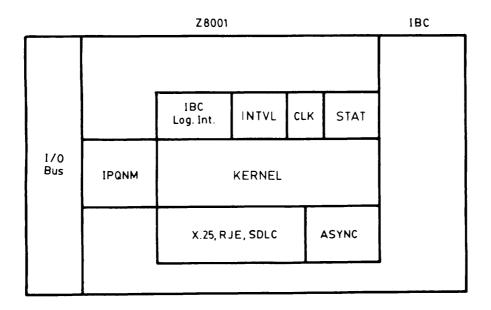

#### ICS2/3 OPERATING SYSTEM

The ICS2/3 OS consists of basically two groups of routines: the kernel operating system and other higher-level processes, such as the following:

- Communication monitors/control processes, such as X.25 and RJE

- Real time clock process (CLK)

- Interval timer process (INIVL)

- OTA handling process

- Boot code

- Status handling software (STAT)

The operating system is based on a multitasking, multipriority timesliced kernel operation, together with additional routines for process-to-process communications, such as IPQNM:

- ICS2/3-to-PRIMOS

- Process-to-process within the boundaries of the ICS2/3

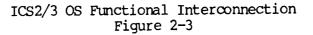

Figure 2-3 illustrates the ICS2/3 OS functional interconnection.

#### The Kernel

The kernel is the lowest level of the operating system structure and is responsible for allocating the resources of the ICS2/3. The ICS2/3 resources consist of the configured memory, the Z8001, and the various interrupts. ICS2 memory is either 128K or 256K bytes, while the ICS3 can have 256K, 512K, or 1024K bytes. The kernel can be considered as part of the processes running underneath the operating system because the kernel tables are shared among all the processes. Kernel code may be executed either on behalf of processes or as part of the actual system. Furthermore, interrupts can occur at any time, even while kernel code is executing; so, kernel data and tables are designed for re-entrant access and modification.

The kernel's primary responsibility is the scheduling of the various processes. Each process is assigned a software priority at process login time, thus allowing the operating system to arbitrate and schedule the processes. The operating system is not responsible for handling I/O operations because each process is responsible for performing its own I/O operations. The kernel does, however, provide standard routines to enable the processes to perform I/O operations correctly.

The kernel has a number of data blocks and linked lists. Each user process consists of a process control block, which contains the process priority; a link to the next process control block; a semaphore pointer; process elapsed time; the current program counter; and saved registers. The kernel maintains a ready list of linked processes ready to be resumed. When a process is to be resumed, the kernel restores the registers, program counter, and flags from the process The ready list is a multipriority list of which there control block. are currently four different priority levels. However, among the process control blocks of the same priority level, dispatching is first-come first-served. When a process has "completed" (which requires the occurrence of a specific event), it waits on a semaphore. The kernel then places the process control block on the appropriate wait list and invokes the next ready process. Note that there is no multiple wait; that is, a process can only sequentially wait on a number of different events. When the event associated with a semaphore (triggered by an interrupt) occurs, the kernel notifies the process by removing it from the wait list and returning it to the ready list.

<u>Process Scheduling</u>: A process or task is the basic logical unit controlled by the operating system. A process, which is a logically complete execution path through the code, may demand the use of the system resources via the kernel routines. A process is not the same thing as a program. A program is merely a section of code, whereas multiple processes may proceed through the same code. The kernel uses a preemptive scheduling algorithm. A running task can be suspended by a higher priority task, by interrupt code (unless the task specifically disables interrupts), or by a system clock that limits the run time of a task (the time slice allocated to that task at login). This scheduling system ensures that no task can capture all the processing time, and that every process gets a chance to run.

The current configuration of the operating system allows 64 processes on four priority levels.

Semaphores: The ICS2/3 OS uses semaphores to synchronize its operation, which results in the following:

- Serialization of all accesses to the state variables, collecting all accesses into the critical regions guarded by that semaphore

- Guarding against illegal transitions

Assigning a semaphore to a process serializes all accesses and protects against illegal transitions; the semaphore is decremented after each critical region that precedes a possible illegal transition. The decremented semaphore will block the process if it was not incremented inside the critical region. Any cases of ambiguity have to be resolved by using the appropriate scheduling discipline. The ICS2/3 employs semaphores for the following:

- Clock and timers

- Time slice

- Login

- Free space lock

- OTAS, INAS

- IBC

- DMX

- LCO, LC1

- IBC error status

- Various other resources, such as queues

Operating System Services: The ICS2/3 OS also contains routines to do the following:

- Allocate/deallocate free memory according to Knuth's boundary control word scheme

- Handle INAs, OTAs, interrupts, DMX, queue manipulation, and process-to-process communications

- Provide logical interrupt and interface capabilities between the IBC and Z8001 code

#### Cold Start

At cold start, PRIMOS initiates the PROM code in the ICS2/3 by issuing an Output Control Pulse (OCP '14). This checks the logic and verifies the Z8001 memory. After checking the Z8001 memory, PRIMOS carries out the downline load. This entails copying the complete downline load file into the Z8001 memory, starting at segment 40H (hex notation). The downline load file consists of the following:

- Z8001 OS and protocol handlers

- Z8001 verify code (runtime verify)

- IBC verify microcode

- Operating IBC microcode

On completion of the diagnostic checks, a 16-word table containing the LAC card cage configuration is sent to PRIMOS. Also, the ICS2/3 software initializes the kernel data bases, which are derived from the table of user processes. These user processes include the following:

- Clock manager

- OTA handling process

- Buffer handling process

- Protocol managers

- Communications monitor/operating system diagnostic process for Prime customer service personnel

- IBC status handling process

#### Warm Start

Warm start enables ICS2/3 recovery after the initial boot. PRIMOS initiates the PROM code in the ICS2/3 by issuing an Output Control Pulse (OCP '17). Warm start is similar to a cold start, except that the PROM code in the Z8001 does not run a full diagnostic test.

#### IBC MICROCODE

The IBC is an intelligent multi-channel DMA (Direct Memory Access) device controlled by a sequencer and ALU (see Chapter 1). It interfaces the Z8001 to the data links via the LAC bus, and also interfaces to/from the Prime memory via the Prime I/O bus.

The IBC microcode is booted by the Z8001 during PRIMOS cold and warm starts. The IBC microcode, when booted, should contain all the protocols that will be used on the ICS2/3. It should include those protocols to be brought up after a PRIMOS cold start.

The Z8001 performs several tasks with respect to the IBC. The first two tasks of configuring IBC pointers and configuring the LAC bus are accomplished during ICS2/3 initialization, that is, before the ICS2/3 operating system is fully up.

First, the Z8001 supplies both primary and secondary status buffers for the IBC. The status buffers are used by the IBC to pass status (for instance, good CRC or bad CRC) back to the Z8001.

Second, the Z8001 must characterize the LAC bus. Characterization of the LAC bus means determining LAC locations and type of LAC.

LACs are of three basic types: ICS2 four-line asynchronous LACs, ICS3 four-line asynchronous LACs, and ICS2/3 two-line synchronous LACs. ICS2 asynchronous LACs use Zilog's Serial Input/Output (SIO) chip, whereas the ICS3 asynchronous LACs use Zilog's Serial Communications Controller (SCC). They have different IDs so the IBC code can identify which type are installed. ICS3-type LACs are usable only on an ICS3, whereas the ICS2 type can be used with either the ICS2 or ICS3 controller board. To characterize the LAC bus, the Z8001 runs channel programs to read the LAC ID registers for each possible backplane slot. It builds a table, mapping physical lines on the LACs as they are found to logical line numbers.

Third, the Z8001 must initialize the MAP RAM, write the line file, and issue the initialize-a-line command for each physical line. For each line, it then runs channel programs to initialize the communications lines to establish protocol type, baud rate, and loop back control. The MAP RAM establishes the mapping between the logical and physical lines. Initialization of a line is the function of the individual protocol handler process and not of the ICS2/3 OS.

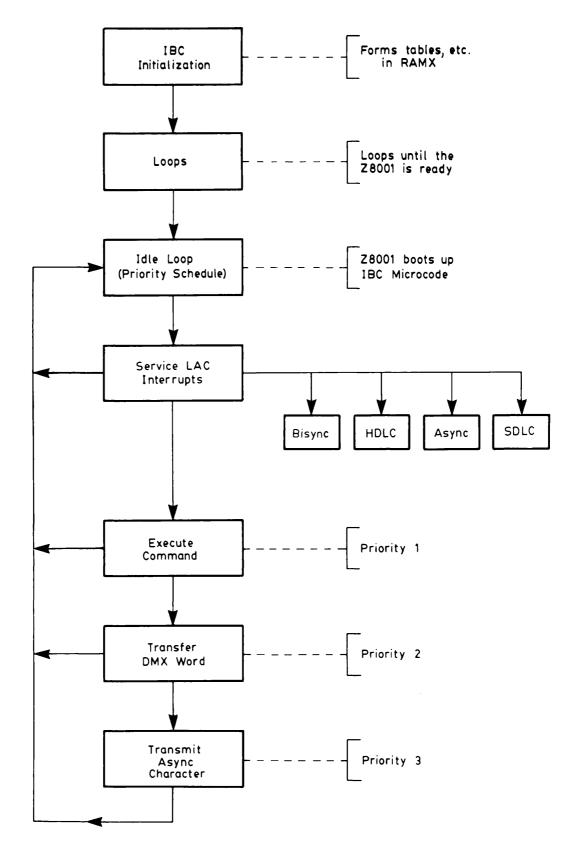

The IBC microcode functional interconnection is shown in Figure 2-4.

#### USER PROTOCOL-SPECIFIC MODULES

At Rev. 20.1, the ICS2 and ICS3 will support HDLC and BSC-framed PRIMENET/X.25, BSC-based RJE, SDLC, and asynchronous protocols. To achieve this, the ICS2/3 software incorporates four types of user protocol-specific software modules:

- X.25 modules

- RJE modules

- SDLC

- Asynchronous modules

Descriptions of the protocol-specific modules are included in the following pages to give the technical reader a basic understanding of the protocol-dependent software in the ICS2/3 and its function. This information is not necessary for the configuration and operation of the ICS2/3.

#### X.25 Protocol-specific Modules

The following text gives brief descriptions of the various X.25 software modules resident in the ICS2/3. Figure 2-5 illustrates the software module interconnection of the ICS2/3 X.25 protocol.

When the ICS2/3 has been booted, it sets up logical connections to the Prime CPU for the maximum number of X.25 lines that can be supported by an ICS2/3, together with a single logical connection to the buffer server process for the purpose of accessing PRIMOS buffers. When the Prime CPU attempts to start up an X.25 line, it places a configuration block on the high priority queue for that line.

The main X.25 process, X25MAIN, is notified of this event, dequeues the block, and attempts to configure the line. If the attempt succeeds, then X25MAIN awaits notification of another event, such as

- A code word from the host

- An X.25 information frame to be transmitted

- An X.25 unnumbered or supervisory frame to be transmitted

- An interrupt received from the IBC for the specific line

- An IBC error

- A buffer received from the host

- A timeout

Overview of the ICS2/3 X.25 Software Figure 2-5

From the item enqueued on the event queue, X25MAIN can determine the cause of the notification and then call the appropriate function to process it.

If the event that caused notification is an X25 frame to be transmitted, then the Z8001 DMXs the frame into ICS2/3 memory and queues the frame for output by the IBC via the appropriate line.

When the IBC receives a frame from the line, the frame is buffered in ICS2/3 memory and the IBC interrupts the Z8001. The Z8001 then DMXs the frame to the host and notifies the host that a good frame is available.

Descriptions of the main ICS2/3 modules follow:

| Module   | Description                                                                                                                                                                                                                                                                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x25mAIN  | This is the main ICS2/3 X.25 process.<br>Its primary purpose is to set up logical<br>connections to the host for each X.25<br>line, and logical connections within the<br>ICS2/3 to the buffer server process, the<br>IBC logical interrupt handling process,<br>and the timer process. |

|          | X25MAIN waits for notification of an<br>event (for example, initialization of a<br>line) or for a block to transmit, and<br>then calls the appropriate routine.                                                                                                                         |

|          | Furthermore, X25MAIN sets up three<br>special queues to enable rapid<br>determination of outstanding buffer<br>requests:                                                                                                                                                                |

|          | • Large PRIMOS buffers                                                                                                                                                                                                                                                                  |

|          | • Small PRIMOS buffers                                                                                                                                                                                                                                                                  |

|          | • ICS2/3 transmit buffers                                                                                                                                                                                                                                                               |

| FROMHOST | This routine processes a notification<br>from the host and decides whether the<br>host has sent a code word, control<br>block, or transmit frame.                                                                                                                                       |

| TXMSG:   | This routine controls the transmission<br>of an X.25 message over the synchronous<br>link.                                                                                                                                                                                              |

| IBC_INI  | This routine initializes the IBC to<br>handle the configuration block for<br>either HDLC or BSC-framed X.25.                                                                                                                                                                            |

| CODE1BLK | This routine configures the specified<br>line by using the control block sent<br>from the host. The host is notified of<br>successful completion of initialization<br>or of any error conditions that are<br>detected.                                                                  |

2-16

Module Description This routine is called by X25MAIN to PHANTOMINTERRUPT process IBC interrupts, namely • A completed frame transmission • A received message • a changed data channel status FLUSH\_XMIT\_O This routine flushes the transmit queue by returning all transmit buffers to the free pool and setting the chain pointer to zero. CET\_BUFFER This routine consists of two functions that obtain a long or short PRIMOS buffer Queue Control Block (OCB)respectively. STATISTICS This routine updates the specified counters block field by 1, and where necessary, updates the interrupt status The ICS2/3 collects large block. numbers of statistics that may be made available to the user in future releases of PRIMOS.

- APPEND\_TX\_CHAIN This routine appends a buffer to the transmit chain that is pointed-to from the Synchronous Line Control Block.

- CTLWORD This routine processes control words sent from the host to the X.25 process on the ICS2/3.

SHORTBUFFER This routine processes short PRIMOS buffers sent from the host.

- DECON This routine is called when a line is ready for complete deconfiguration; that is, when there are no outstanding requirements for host buffers.

- LONGBUFFER This routine processes long PRIMOS buffers sent from the host.

- TIMEOUT This routine is called when X25MAIN receives notification of a timeout.

DUMP\_COUNTERS This routine dumps counters to the host using large PRIMOS buffers.

| Module               | Description                                                                                                                                                                        |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICS2_FATAL_IBC_ERROR | This routine handles any serious IBC<br>errors by emptying the transmit and<br>receive chains of all lines, returning<br>the buffers to the free pool, and<br>resetting the lines. |

| CODE_WORD            | This routine sends a code word to the<br>host by enqueuing the code word on the<br>host's high priority queue.                                                                     |

| UPD_NR               | This routine updates the N(R) fields in all the buffers queued for transmission by the IBC.                                                                                        |

| UPD_INTS             | This routine inserts a character into<br>the interrupt status block. When the<br>block becomes full, it attempts to DMX<br>it to the host.                                         |

| DUMP_INTERRUPTS      | This routine dumps the interrupt block to the host.                                                                                                                                |

First Edition

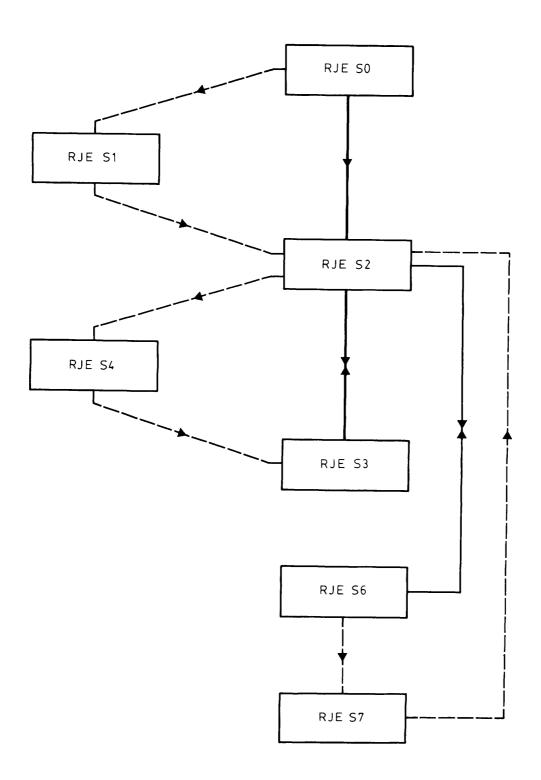

# RJE Protocol-specific Modules

The following paragraphs provide a simplified explanation of the RJE logic in the ICS2/3. This description does not apply to PRIME/SNA RJE.

RJE in the ICS2/3 is a collection of state-driven modules. Logical states are changed when particular events occur, such as

- A block sent from PRIMOS

- Data Set Status (DSS) changing

- IBC-controlled line activity, such as, transmit completion, receive starting, and receive completion.

When an RJE session starts, PRIMOS establishes a logical connection with the ICS2/3 RJE process and sends a configuration block for the line concerned. This configuration block is validated and a configuration-accepted response is returned to PRIMOS.

Once the line configuration has been accepted, either PRIMOS or the remote host can send data; whichever end starts sending data causes the logic to "flip-flop" between transmit and receive states. This reflects the half-duplex nature of RJE protocols.

For example, if PRIMOS sends the ICS2/3 a block, it will be transmitted, and then the ICS2/3 RJE process will look for receive data. When input from the line occurs, the received data/response is sent to PRIMOS, and the software waits for another block from PRIMOS.

Responsibility for detailed checking of protocol violations is left with the appropriate RJE support in PRIMOS; the ICS2/3 is concerned only with receiving and transmitting data which conforms to general RJE-defined formats.

When the RJE session is completed, PRIMOS sends a deconfigure command, and the ICS2/3 releases the line for use by other protocols.

The following sections briefly describe the RJE software modules which reside in the ICS2/3.